# AM08X5 Real-Time Clock Family

#### **Features**

- Ultra-low supply current (all at 3V):

- 14 nA with RC oscillator

- 22 nA with RC oscillator and Autocalibration

- 55 nA with crystal oscillator

- Baseline timekeeping features:

- 32.768 kHz crystal oscillator with integrated load capacitor/resistor

- Counters for hundredths, seconds, minutes, hours, date, month, year, century, and weekday

- Alarm capability on all counters

- Programmable output clock generation (32.768 kHz to 1 year)

- Countdown timer with repeat function

- Automatic leap year calculation

- Advanced timekeeping features:

- Integrated power optimized RC oscillator

- Advanced crystal calibration to ± 2 ppm

- Advanced RC calibration to ± 16 ppm

- Automatic calibration of RC oscillator to crystal oscillator

- Watchdog timer with hardware reset

- 256 bytes of general purpose RAM

- Power management features:

- Automatic switchover to VBAT

- External interrupt monitor

- Programmable low battery detection threshold

- Programmable analog voltage comparator

- I<sup>2</sup>C (up to 400 kHz) and 3-wire or 4-wire SPI (up to 2 MHz) serial interfaces available

- Operating voltage 1.5-3.6 V

- Clock and RAM retention voltage 1.5-3.6 V

- Operating temperature –40 to 85 °C

- All inputs include Schmitt Triggers

- 3x3 mm QFN-16 package

## **Applications**

- Smart cards

- Wireless sensors and tags

- Medical electronics

- Utility meters

- Data loggers

- Appliances

- Handsets

- Consumer electronics

- Communications equipment

### **Description**

The Ambiq Micro AM08X5 Real-Time Clock family provides a groundbreaking combination of ultra-low power coupled with a highly sophisticated feature set. With power requirements significantly lower than any other industry RTC (as low as 14 nA), these are the first semiconductors based on Ambiq Micro's innovative SPOT<sup>TM</sup> (Subthreshold Power Optimized Technology) CMOS platform. The AM08X5 includes on-chip oscillators to provide minimum power consumption, full RTC functions including battery backup and programmable counters and alarms for timer and watchdog functions, and either an I<sup>2</sup>C or SPI serial interface for communication with a host controller.

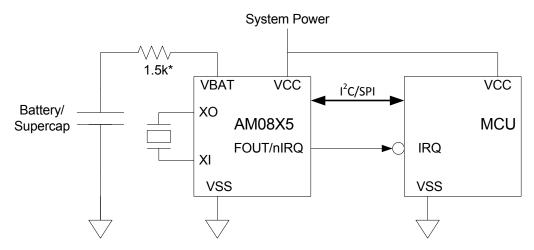

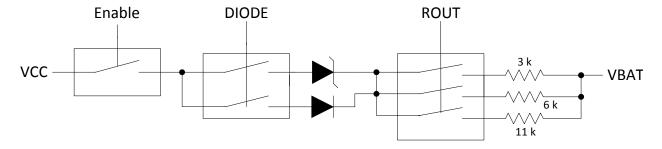

## **Typical Application Circuit**

<sup>\*</sup> Total battery series impedance = 1.5k ohms, which may require an external resistor

## **Contents**

| 1. | Family Summary                                      | . 11 |

|----|-----------------------------------------------------|------|

| 2. | Package Pins                                        | . 11 |

|    | 2.1. Pin Configuration and Connections              |      |

|    | 2.2. Pin Descriptions                               | . 12 |

| 3. | Digital Architecture Summary                        | . 13 |

| 4. | Electrical Specifications                           | . 14 |

|    | 4.1. Absolute Maximum Ratings                       | . 14 |

|    | 4.2. Power Supply Parameters                        |      |

|    | 4.3. Operating Parameters                           | . 16 |

|    | 4.4. Oscillator Parameters                          | . 18 |

|    | 4.5. V <sub>CC</sub> Supply Current                 | 20   |

|    | 4.6. V <sub>BAT</sub> Supply Current                |      |

|    | 4.7. BREF Electrical Characteristics                |      |

|    | 4.8. I <sup>2</sup> C AC Electrical Characteristics |      |

|    | 4.9. SPI AC Electrical Characteristics              |      |

|    | 4.10. Power On AC Electrical Characteristics        | . 30 |

| 5. | Functional Description                              | 31   |

|    | 5.1. I <sup>2</sup> C Interface                     | 32   |

|    | 5.1.1. Bus Not Busy                                 | 32   |

|    | 5.1.2. Start Data Transfer                          | 33   |

|    | 5.1.3. Stop Data Transfer                           | 33   |

|    | 5.1.4. Data Valid                                   |      |

|    | 5.1.5. Acknowledge                                  |      |

|    | 5.1.6. Offset Address Transmission                  |      |

|    | 5.1.7. Write Operation                              |      |

|    | 5.1.8. Read Operation                               |      |

|    | 5.2. SPI Interface                                  |      |

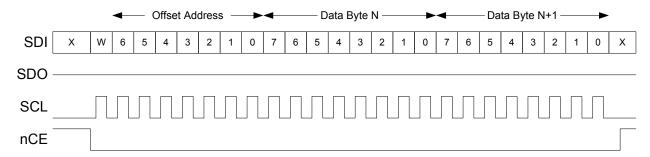

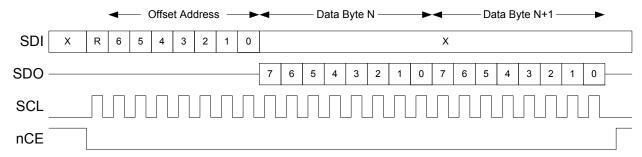

|    | 5.2.1. Write Operation                              |      |

|    | 5.2.2. Read Operation                               |      |

|    | 5.3. XT Oscillator                                  |      |

|    | 5.4. RC Oscillator                                  |      |

|    | 5.5. RTC Counter Access                             |      |

|    | 5.6. Hundredths Synchronization                     |      |

|    | 5.7. Generating Hundredths of a Second              |      |

|    | 5.9. Digital Calibration                            |      |

|    | 5.9.1. XT Oscillator Digital Calibration            |      |

|    | 5.9.2. RC Oscillator Digital Calibration            |      |

|    | 5.10. Autocalibration                               |      |

|    | 5.10.1. Autocalibration Operation                   |      |

|    | 5.10.2. XT Autocalibration Mode                     |      |

|    | 5.10.3. RC Autocalibration Mode                     |      |

|    | 5.10.4. Autocalibration Frequency and Control       |      |

|    | 5.10.5. Autocalibration Filter (AF) Pin             |      |

|    | 5.10.6. Autocalibration Fail                        |      |

|    | 5.11. Oscillator Failure Detection                  |      |

|    | 5.12. Interrupts                                    |      |

|    | 5.12.1. Interrupt Summary                           |      |

|    | 5.12.2. Alarm Interrupt AIRQ                        |      |

|    | 5.12.3. Countdown Timer Interrupt TIRQ       | . 42 |

|----|----------------------------------------------|------|

|    | 5.12.4. Watchdog Timer Interrupt WIRQ        | . 42 |

|    | 5.12.5. Battery Low Interrupt BLIRQ          | . 42 |

|    | 5.12.6. External Interrupts X1IRQ and X2IRQ  | . 42 |

|    | 5.12.7. Oscillator Fail Interrupt OFIRQ      |      |

|    | 5.12.8. Autocalibration Fail Interrupt ACIRQ | . 43 |

|    | 5.12.9. Servicing Interrupts                 | . 43 |

|    | 5.13. Power Control and Switching            |      |

|    | 5.13.1. Battery Low Flag and Interrupt       |      |

|    | 5.13.2. Analog Comparator                    |      |

|    | 5.13.3. Pin Control and Leakage Management   |      |

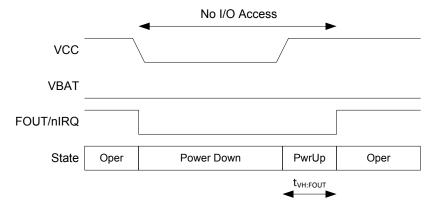

|    | 5.13.4. Power Up Timing                      |      |

|    | 5.14. Software Reset                         |      |

|    | 5.15. Trickle Charger                        |      |

|    | •                                            |      |

| 6. | Registers                                    |      |

|    | 6.1. Register Definitions and Memory Map     |      |

|    | 6.2. Time and Date Registers                 |      |

|    | 6.2.1. 0x00 - Hundredths                     | . 49 |

|    | 6.2.2. 0x01 - Seconds                        | . 49 |

|    | 6.2.3. 0x02 - Minutes                        | . 50 |

|    | 6.2.4. 0x03 - Hours                          | . 50 |

|    | 6.2.5. 0x04 - Date                           | . 51 |

|    | 6.2.6. 0x05 - Months                         | . 51 |

|    | 6.2.7. 0x06 - Years                          | . 52 |

|    | 6.2.8. 0x07 - Weekday                        | . 52 |

|    | 6.3. Alarm Registers                         | . 53 |

|    | 6.3.1. 0x08 - Hundredths Alarm               | . 53 |

|    | 6.3.2. 0x09 - Seconds Alarm                  |      |

|    | 6.3.3. 0x0A - Minutes Alarm                  | . 54 |

|    | 6.3.4. 0x0B - Hours Alarm                    | . 54 |

|    | 6.3.5. 0x0C - Date Alarm                     | . 55 |

|    | 6.3.6. 0x0D - Months Alarm                   |      |

|    | 6.3.7. 0x0E - Weekday Alarm                  | . 56 |

|    | 6.4. Configuration Registers                 | . 57 |

|    | 6.4.1. 0x0F - Status (Read Only)             |      |

|    | 6.4.2. 0x10 - Control1                       | . 58 |

|    | 6.4.3. 0x11 - Control2                       | . 58 |

|    | 6.4.4. 0x12 - Interrupt Mask                 | . 59 |

|    | 6.4.5. 0x13 - SQW                            | . 60 |

|    | 6.5. Calibration Registers                   | . 62 |

|    | 6.5.1. 0x14 - Calibration XT                 | . 62 |

|    | 6.5.2. 0x15 - Calibration RC Upper           | . 62 |

|    | 6.5.3. 0x16 - Calibration RC Lower           | . 63 |

|    | 6.6. Interrupt Polarity Control Register     | . 63 |

|    | 6.6.1. 0x17 - Interrupt Polarity Control     | . 63 |

|    | 6.7. Timer Registers                         |      |

|    | 6.7.1. 0x18 - Countdown Timer Control        |      |

|    | 6.7.2. 0x19 - Countdown Timer                | . 66 |

|    | 6.7.3. 0x1A - Timer Initial Value            | . 66 |

|    | 6.7.4. 0x1B - Watchdog Timer                 | . 66 |

|    | 6.8. Oscillator Registers                    |      |

|    | 6.8.1. 0x1C - Oscillator Control             | . 67 |

|    | 6.8.2. 0x1D – Oscillator Status Register     | . 68 |

|    | 6.9. Miscellaneous Registers                                | 68 |

|----|-------------------------------------------------------------|----|

|    | 6.9.1. 0x1F - Configuration Key                             |    |

|    | 6.10. Analog Control Registers                              | 69 |

|    | 6.10.1. 0x20 - Trickle                                      | 69 |

|    | 6.10.2. 0x21 - BREF Control                                 | 70 |

|    | 6.10.3. 0x26 – AFCTRL                                       | 70 |

|    | 6.10.4. 0x27 – Batmode IO Register                          |    |

|    | 6.10.5. 0x2F – Analog Status Register (Read Only)           | 71 |

|    | 6.10.6. 0x30 – Output Control Register                      | 72 |

|    | 6.11. ID Registers                                          |    |

|    | 6.11.1. 0x28 – ID0 - Part Number Upper Register (Read Only) | 72 |

|    | 6.11.2. 0x29 – ID1 - Part Number Lower Register (Read Only) | 73 |

|    | 6.11.3. 0x2A – ID2 - Part Revision (Read Only)              |    |

|    | 6.11.4. 0x2B – ID3 – Lot Lower (Read Only)                  | 73 |

|    | 6.11.5. 0x2C – ID4 – ID Upper (Read Only)                   |    |

|    | 6.11.6. 0x2D – ID5 – Unique Lower (Read Only)               |    |

|    | 6.11.7. 0x2E – ID6 – Wafer (Read Only)                      |    |

|    | 6.12. Ram Registers                                         |    |

|    | 6.12.1. 0x3F - Extension RAM Address                        |    |

|    | 6.12.2. 0x40 - 0x7F – Standard RAM                          |    |

|    | 6.12.3. 0x80 - 0xFF – Alternate RAM                         | 75 |

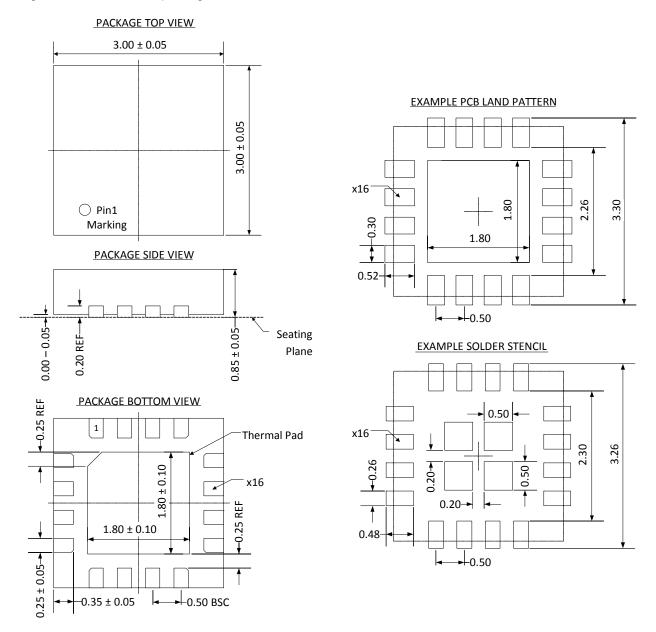

| 7. | Package Mechanical Information                              | 76 |

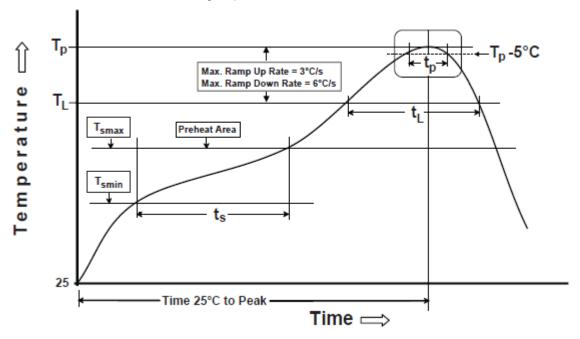

| 8. | Reflow Profile                                              | 77 |

| 9. | Ordering Information                                        | 78 |

| 10 | . Document Revision History                                 | 78 |

| 11 | . Contact Information                                       | 80 |

| 12 | . Legal Information and Disclaimers                         | QΛ |

| 12 | . Legai illioilliation alla Discialilleis                   |    |

## **List of Figures**

| Figure 1. Pin Configuration Diagram                                                   | 11 |

|---------------------------------------------------------------------------------------|----|

| Figure 2. Digital Architecture Summary                                                | 14 |

| Figure 3. Power Supply Switchover                                                     |    |

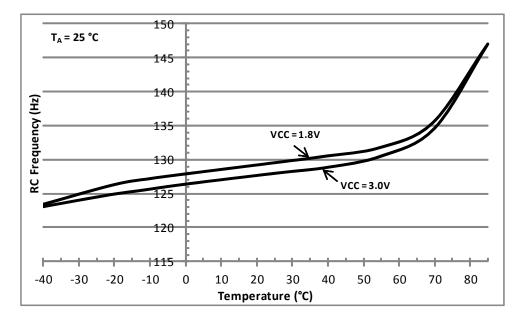

| Figure 4. Calibrated RC Oscillator Typical Frequency Variation vs. Temperature        | 19 |

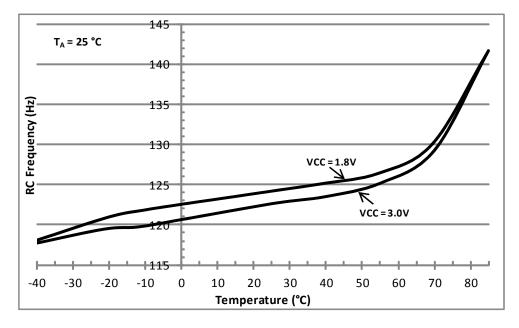

| Figure 5. Uncalibrated RC Oscillator Typical Frequency Variation vs. Temperature      | 19 |

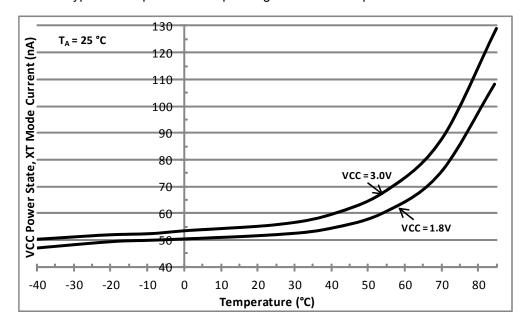

| Figure 6. Typical VCC Current vs. Temperature in XT Mode                              | 21 |

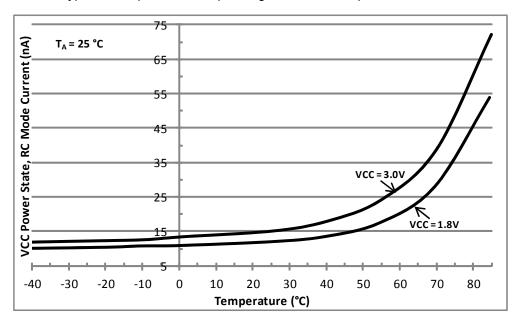

| Figure 7. Typical VCC Current vs. Temperature in RC Mode                              |    |

| Figure 8. Typical VCC Current vs. Temperature in RC Autocalibration Mode              | 22 |

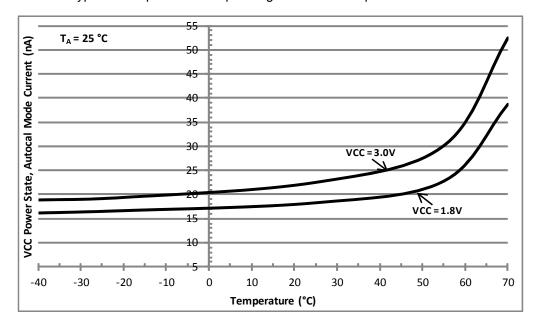

| Figure 9. Typical VCC Current vs. Voltage, Different Modes of Operation               | 22 |

| Figure 10. Typical VCC Current vs. Voltage, I <sup>2</sup> C and SPI Burst Read/Write | 23 |

| Figure 11. Typical VCC Current vs. Voltage, 32.768 kHz Clock Output                   | 23 |

| Figure 12. Typical VBAT Current vs. Temperature in XT Mode                            |    |

| Figure 13. Typical VBAT Current vs. Temperature in RC Mode                            |    |

| Figure 14. Typical VBAT Current vs. Temperature in RC Autocalibration Mode            |    |

| Figure 15. Typical VBAT Current vs. Voltage, Different Modes of Operation             |    |

| Figure 16. Typical VBAT Current vs. Voltage in VCC Power State                        |    |

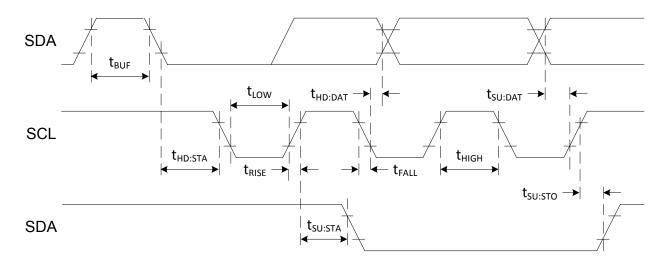

| Figure 17. I <sup>2</sup> C AC Parameter Definitions                                  |    |

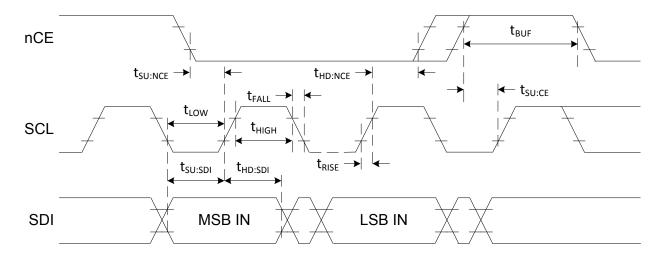

| Figure 18. SPI AC Parameter Definitions – Input                                       |    |

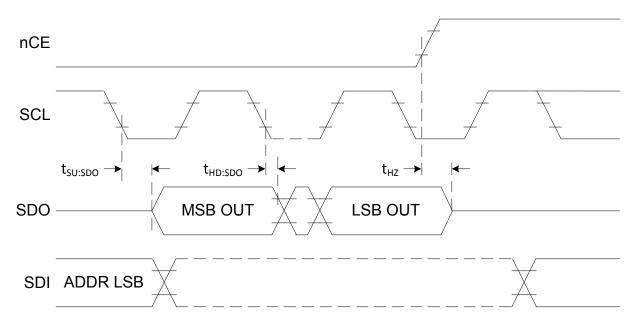

| Figure 19. SPI AC Parameter Definitions – Output                                      | 29 |

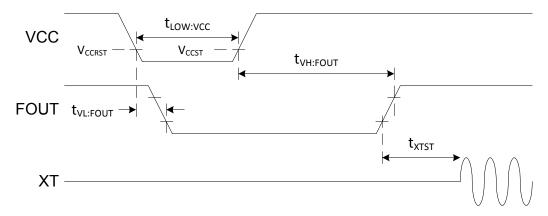

| Figure 20. Power On AC Electrical Characteristics                                     |    |

| Figure 21                                                                             |    |

| Figure 22. Detailed Block Diagram                                                     | 31 |

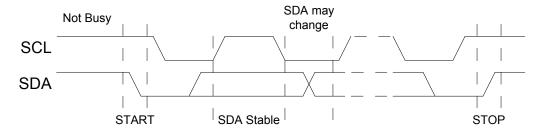

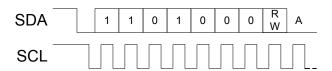

| Figure 23. Basic I <sup>2</sup> C Conditions                                          |    |

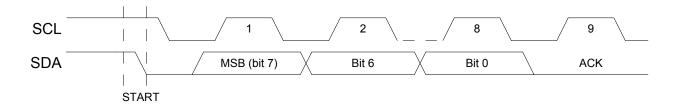

| Figure 24. I <sup>2</sup> C Acknowledge Address Operation                             |    |

| Figure 25. I <sup>2</sup> C Address Operation                                         | 34 |

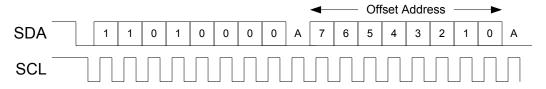

| Figure 26. I <sup>2</sup> C Offset Address Transmission                               |    |

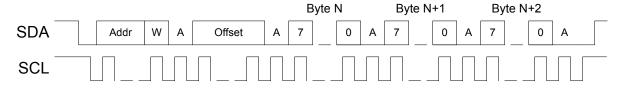

| Figure 27. I <sup>2</sup> C Write Operation                                           |    |

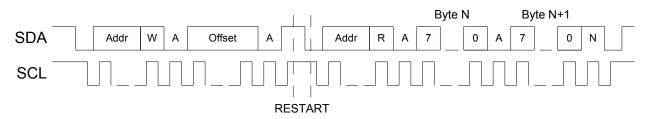

| Figure 28. I <sup>2</sup> C Read Operation                                            |    |

| Figure 29. SPI Write Operation                                                        |    |

| Figure 30. SPI Read Operation                                                         |    |

| Figure 31. Power States                                                               |    |

| Figure 32. Power Up Timing                                                            |    |

| Figure 33. Trickle Charger                                                            |    |

| Figure 34. Package Mechanical Diagram                                                 |    |

| Figure 35. Reflow Soldering Diagram                                                   | 77 |

## **List of Tables**

| Table 53: \$ | Status Register Bits                     | 57 |

|--------------|------------------------------------------|----|

| Table 54: 0  | Control1 Register                        | 58 |

|              | Control1 Register Bits                   |    |

| Table 56: 0  | Control2 Register                        | 58 |

| Table 57: 0  | Control2 Register Bits                   | 58 |

| Table 58: r  | nIRQ2 Pin Control                        | 59 |

| Table 59: I  | FOUT/nIRQ Pin Control                    | 59 |

| Table 60: I  | Interrupt Mask Register                  | 59 |

| Table 61: I  | Interrupt Mask Register Bits             | 59 |

|              | SQW Register                             |    |

|              | SQW Register Bits                        |    |

| Table 64: \$ | Square Wave Function Select              | 61 |

| Table 65: 0  | Calibration XT Register                  | 62 |

|              | Calibration XT Register Bits             |    |

|              | Calibration RC Upper Register            |    |

| Table 68: 0  | Calibration RC Upper Register Bits       | 62 |

|              | CMDR Function                            |    |

|              | Calibration RC Lower Register            |    |

|              | Calibration RC Lower Register Bits       |    |

| Table 72: I  | Interrupt Polarity Control Register      | 63 |

| Table 73: I  | Interrupt Polarity Control Register Bits | 63 |

|              | Countdown Timer Control Register         |    |

| Table 75: 0  | Countdown Timer Control Register Bits    | 64 |

|              | Repeat Function                          |    |

| Table 77: 0  | Countdown Timer Function Select          | 65 |

|              | Countdown Timer Register                 |    |

|              | Countdown Timer Register Bits            |    |

| Table 80:    | Timer Initial Value Register             | 66 |

| Table 81:    | Timer Initial Value Register Bits        | 66 |

| Table 82: \  | Watchdog Timer Register                  | 66 |

| Table 83: \  | Watchdog Timer Register Bits             | 67 |

| Table 84: \  | Watchdog Timer Frequency Select          | 67 |

|              | Oscillator Control Register              |    |

| Table 86: 0  | Oscillator Control Register Bits         | 67 |

| Table 87: 0  | Oscillator Status Register               | 68 |

|              | Oscillator Status Register Bits          |    |

|              | Configuration Key Register               | 68 |

| Table 90: 0  | Configuration Key Register Bits          | 69 |

|              | Trickle Register                         |    |

| Table 92:    | Trickle Register Bits                    | 69 |

|              | Trickle Charge Output Resistor           |    |

|              | BREF Control Register                    |    |

| Table 95: I  | BREF Control Register Bits               | 70 |

|              | VBAT Reference Voltage                   |    |

|              | AFCTRL Register                          |    |

|              | AFCTRL Register Bits                     |    |

|              | Batmode IO Register                      |    |

|              | : Batmode IO Register Bits               |    |

|              | : Analog Status Register                 |    |

|              | : Analog Status Register Bits            |    |

|              | : Output Control Register                |    |

| Table 104:   | : Output Control Register Bits           | 72 |

|              | : 28 – ID0 – Part Number Upper Register  |    |

| Table 106:   | : 28 – ID1 – Part Number Lower Register  | 73 |

| Table 108: 2A – ID2 – Part Revision Register Bits       73         Table 109: 2B – ID3 – Lot Lower Register       73         Table 110: 2B – ID3 – Lot Lower Register Bits       73         Table 111: 2C – ID4 – ID Upper Register       74         Table 112: 2C – ID4 – ID Upper Register Bits       74         Table 113: 2D – ID5 – ID Lower Register       74         Table 114: 2D – ID5 – ID Lower Register Bits       74         Table 115: 2E – ID6 – Wafer Register       74         Table 116: 2E – ID6 – Wafer Register Bits       75         Table 117: 3F – Extension RAM Address Register       75         Table 118: 3F – Extension RAM Address Register Bits       75         Table 119: Reflow Soldering Requirements       75         Table 120: Ordering Information       78         Table 121: Document Revision History       78 | Table 107: 2 | 2A – ID2 – Part Revision Register7       | '3         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------------------------|------------|

| Table 110: 2B – ID3 – Lot Lower Register Bits       73         Table 111: 2C – ID4 – ID Upper Register       74         Table 112: 2C – ID4 – ID Upper Register Bits       74         Table 113: 2D – ID5 – ID Lower Register       74         Table 114: 2D – ID5 – ID Lower Register Bits       74         Table 115: 2E – ID6 – Wafer Register       74         Table 116: 2E – ID6 – Wafer Register Bits       75         Table 117: 3F – Extension RAM Address Register       75         Table 118: 3F – Extension RAM Address Register Bits       75         Table 119: Reflow Soldering Requirements       77         Table 120: Ordering Information       78                                                                                                                                                                                    | Table 108: 2 | 2A – ID2 – Part Revision Register Bits   | '3         |

| Table 110: 2B – ID3 – Lot Lower Register Bits       73         Table 111: 2C – ID4 – ID Upper Register       74         Table 112: 2C – ID4 – ID Upper Register Bits       74         Table 113: 2D – ID5 – ID Lower Register       74         Table 114: 2D – ID5 – ID Lower Register Bits       74         Table 115: 2E – ID6 – Wafer Register       74         Table 116: 2E – ID6 – Wafer Register Bits       75         Table 117: 3F – Extension RAM Address Register       75         Table 118: 3F – Extension RAM Address Register Bits       75         Table 119: Reflow Soldering Requirements       77         Table 120: Ordering Information       78                                                                                                                                                                                    | Table 109: 2 | PB – ID3 – Lot Lower Register            | '3         |

| Table 112: 2C - ID4 - ID Upper Register Bits       74         Table 113: 2D - ID5 - ID Lower Register       74         Table 114: 2D - ID5 - ID Lower Register Bits       74         Table 115: 2E - ID6 - Wafer Register       74         Table 116: 2E - ID6 - Wafer Register Bits       75         Table 117: 3F - Extension RAM Address Register       75         Table 118: 3F - Extension RAM Address Register Bits       75         Table 119: Reflow Soldering Requirements       77         Table 120: Ordering Information       78                                                                                                                                                                                                                                                                                                            |              |                                          |            |

| Table 113: 2D – ID5 – ID Lower Register       74         Table 114: 2D – ID5 – ID Lower Register Bits       74         Table 115: 2E – ID6 – Wafer Register       74         Table 116: 2E – ID6 – Wafer Register Bits       75         Table 117: 3F – Extension RAM Address Register       75         Table 118: 3F – Extension RAM Address Register Bits       75         Table 119: Reflow Soldering Requirements       77         Table 120: Ordering Information       78                                                                                                                                                                                                                                                                                                                                                                          | Table 111: 2 | 2C – ID4 – ID Upper Register             | <b>'</b> 4 |

| Table 114: 2D – ID5 – ID Lower Register Bits       74         Table 115: 2E – ID6 – Wafer Register       74         Table 116: 2E – ID6 – Wafer Register Bits       75         Table 117: 3F – Extension RAM Address Register       75         Table 118: 3F – Extension RAM Address Register Bits       75         Table 119: Reflow Soldering Requirements       77         Table 120: Ordering Information       78                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 112: 2 | 2C – ID4 – ID Upper Register Bits        | <b>'</b> 4 |

| Table 115: 2E – ID6 – Wafer Register       74         Table 116: 2E – ID6 – Wafer Register Bits       75         Table 117: 3F – Extension RAM Address Register       75         Table 118: 3F – Extension RAM Address Register Bits       75         Table 119: Reflow Soldering Requirements       77         Table 120: Ordering Information       78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Table 113: 2 | 2D – ID5 – ID Lower Register             | <b>'</b> 4 |

| Table 116: 2E - ID6 - Wafer Register Bits75Table 117: 3F - Extension RAM Address Register75Table 118: 3F - Extension RAM Address Register Bits75Table 119: Reflow Soldering Requirements77Table 120: Ordering Information78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Table 114: 2 | 2D – ID5 – ID Lower Register Bits        | ′4         |

| Table 117: 3F – Extension RAM Address Register75Table 118: 3F – Extension RAM Address Register Bits75Table 119: Reflow Soldering Requirements77Table 120: Ordering Information78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 115: 2 | 2E – ID6 – Wafer Register                | 4          |

| Table 118: 3F – Extension RAM Address Register Bits75Table 119: Reflow Soldering Requirements77Table 120: Ordering Information78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Table 116: 2 | PE – ID6 – Wafer Register Bits           | '5         |

| Table 119: Reflow Soldering Requirements    77      Table 120: Ordering Information    78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |              |                                          |            |

| Table 120: Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Table 118: 3 | BF – Extension RAM Address Register Bits | '5         |

| · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Table 119: F | Reflow Soldering Requirements            | 7          |

| Table 121: Document Revision History78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 120: C | Ordering Information                     | '8         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |              | · · · · · · · · · · · · · · · · · · ·    |            |

## 1. Family Summary

The AM08X5 family consists of several members (see Table 1). All devices are supplied in a standard 3x3 mm QFN-16 package. Members of the software and pin compatible AM18X5 RTC with Power Management family are also listed.

|        |                                                      | aseline<br>ekeeping        |           | Advanced 1               | imekeepi      | ng         |                | Power Ma      | nagem      | ent                              |                  |

|--------|------------------------------------------------------|----------------------------|-----------|--------------------------|---------------|------------|----------------|---------------|------------|----------------------------------|------------------|

| Part # | XT<br>Osc                                            | Number<br>of GP<br>Outputs | RC<br>Osc | Calib/<br>Auto-<br>calib | Watch-<br>dog | RAM<br>(B) | VBAT<br>Switch | Reset<br>Mgmt | Ext<br>Int | Power<br>Switch and<br>Sleep FSM | Interface        |

| AM0805 | •                                                    | 3                          |           | •                        | •             | 256        | •              |               | •          |                                  | I <sup>2</sup> C |

| AM0815 | •                                                    | 2                          | •         | •                        | •             | 256        | •              |               | •          |                                  | SPI              |

|        | Software and Pin Compatible AM18X5 Family Components |                            |           |                          |               |            |                |               |            |                                  |                  |

| AM1805 | •                                                    | 4                          | •         | •                        | •             | 256        | •              | -             | -          | •                                | I <sup>2</sup> C |

| AM1815 |                                                      | 3                          |           | •                        | •             | 256        | •              | •             | •          | •                                | SPI              |

**Table 1: Family Summary**

## 2. Package Pins

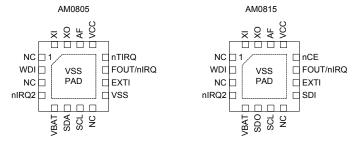

### 2.1 Pin Configuration and Connections

Figure 1 and Table 2 show the QFN-16 pin configurations for the AM08X5 parts. Pins labeled NC must be left unconnected. The thermal pad, pin 17, on the QFN-16 packages must be connected to VSS.

Figure 1. Pin Configuration Diagram

**Table 2: Pin Connections**

| Pin Name    | Pin Type  | Function               | Pin Number |        |  |

|-------------|-----------|------------------------|------------|--------|--|

| riii Naille | riii iype | Function               | AM0805     | AM0815 |  |

| VSS         | Power     | Ground                 | 9,17       | 17     |  |

| VCC         | Power     | System power supply    | 13         | 13     |  |

| XI          | XT        | Crystal input          | 16         | 16     |  |

| ХО          | XT        | Crystal output         | 15         | 15     |  |

| AF          | Output    | Autocalibration filter | 14         | 14     |  |

**Table 2: Pin Connections**

| Pin Name  | Din Tuno | Function                                | Pin Number |        |  |

|-----------|----------|-----------------------------------------|------------|--------|--|

| Fill Name | Pin Type | Function                                | AM0805     | AM0815 |  |

| VBAT      | Power    | Battery power supply                    | 5          | 5      |  |

| SCL       | Input    | I <sup>2</sup> C or SPI interface clock | 7          | 7      |  |

| SDO       | Output   | SPI data output                         |            | 6      |  |

| SDI       | Input    | SPI data input                          |            | 9      |  |

| nCE       | Input    | SPI chip select                         |            | 12     |  |

| SDA       | Input    | I <sup>2</sup> C data input/output      | 6          |        |  |

| EXTI      | Input    | External interrupt input                | 10         | 10     |  |

| WDI       | Input    | Watchdog reset input                    | 2          | 2      |  |

| FOUT/nIRQ | Output   | Int 1/function output                   | 11         | 11     |  |

| nIRQ2     | Output   | Int 2 output                            | 4          | 4      |  |

| nTIRQ     | Output   | Timer interrupt output                  | 12         |        |  |

## 2.2 Pin Descriptions

Table 3 provides a description of the pin connections.

**Table 3: Pin Descriptions**

| Pin Name                                              | Description                                                                                                                                                                                                                                                      |

|-------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSS                                                   | Ground connection. In the QFN-16 packages the ground slug on the bottom of the package must be connected to VSS.                                                                                                                                                 |

| VCC                                                   | Primary power connection. If a single power supply is used, it must be connected to VCC.                                                                                                                                                                         |

| VBAT                                                  | Battery backup power connection. If a backup battery is not present, VBAT must be connected directly to VSS, but it may also be used to provide the analog input to the internal comparator (see Analog-Comparator).                                             |

| XI                                                    | Crystal oscillator input connection.                                                                                                                                                                                                                             |

| XO                                                    | Crystal oscillator output connection.                                                                                                                                                                                                                            |

| AF                                                    | Autocalibration filter connection. A 47pF ceramic capacitor must be placed between this pin and VSS for improved Autocalibration mode timing accuracy.                                                                                                           |

| SCL                                                   | I/O interface clock connection. It provides the SCL input in both I <sup>2</sup> C and SPI interface parts. A pull-up resistor is required on this pin.                                                                                                          |

| SDA (only available in I <sup>2</sup> C environments) | I/O interface I <sup>2</sup> C data connection. A pull-up resistor is required on this pin                                                                                                                                                                       |

| SDO (only available in SPI environments)              | I/O interface SPI data output connection.                                                                                                                                                                                                                        |

| SDI                                                   | I/O interface SPI data input connection.                                                                                                                                                                                                                         |

| nCE (only available in SPI environments)              | I/O interface SPI chip select input connection. It is an active low signal. A pull-up resistor is recommended to be connected to this pin to ensure it is not floating. A pull-up resistor also prevents inadvertent writes to the RTC during power transitions. |

**Table 3: Pin Descriptions**

| Pin Name                                                                                                                                                                                                                                                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| EXTI                                                                                                                                                                                                                                                                  | External interrupt input connection. It may be used to generate an External 1 interrupt with polarity selected by the EX1P bit if enabled by the EX1E bit. The value of the EXTI pin may be read in the EXIN register bit. This pin does not have an internal pull-up or pull-down resistor and so one must be added externally. It must not be left floating or the RTC may consume higher current. Instead, it must be connected directly to either VCC or VSS if not used.                                                                                                                                                                |  |  |  |  |  |

| WDI                                                                                                                                                                                                                                                                   | Watchdog Timer reset input connection. It may also be used to generate an External 2 interrupt with polarity selected by the EX2P bit if enabled by the EX2E bit. The value of the WDI pin may be read in the WDIN register bit. This pin does not have an internal pull-up or pull-down resistor and so one must be added externally. It must not be left floating or the RTC may consume higher current. Instead, it must be connected directly to either VCC or VSS if not used.                                                                                                                                                          |  |  |  |  |  |

| FOUT/nIRQ                                                                                                                                                                                                                                                             | Primary interrupt output connection. This pin is an open drain output. An external pull-up resistor must be added to this pin. It should be connected to the host device and is used to indicate when the RTC can be accessed via the serial interface. FOUT/nIRQ may be configured to generate several signals as a function of the OUT1S field. (see 0x11 - Control2). FOUT/nIRQ is also asserted low on a power up until the AM08X5 has exited the reset state and is accessible via the I/O interface.                                                                                                                                   |  |  |  |  |  |

|                                                                                                                                                                                                                                                                       | <ol> <li>FOUT/nIRQ can drive the value of the OUT bit.</li> <li>FOUT/nIRQ can drive the inverse of the combined interrupt signal IRQ (see Interrupts).</li> <li>FOUT/nIRQ can drive the square wave output (see 0x13 - SQW) if enabled by SQWE.</li> <li>FOUT/nIRQ can drive the inverse of the alarm interrupt signal AIRQ (see Interrupts).</li> </ol>                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| nIRQ2                                                                                                                                                                                                                                                                 | <ol> <li>Secondary interrupt output connection. It is an open drain output. This pin can be left floating if not used. nIRQ2 may be configured to generate several signals as a function of the OUT2S field (see 0x11 - Control2).nIRQ2 can drive the value of the OUTB bit.</li> <li>nIRQ2 can drive the square wave output (see 0x13 - SQW) if enabled by SQWE.</li> <li>nIRQ2 can drive the inverse of the combined interrupt signal IRQ (see Interrupts).</li> <li>nIRQ2 can drive the inverse of the alarm interrupt signal AIRQ (see Interrupts).</li> <li>nIRQ2 can drive either sense of the timer interrupt signal TIRQ.</li> </ol> |  |  |  |  |  |

| nTIRQ (only available in I <sup>2</sup> C environments)  Timer interrupt output connection. It is an open drain output. nTIRQ always drives the a signal. If this pin is used, an external pull-up resistor must be added to this pin. If the p can be left floating. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

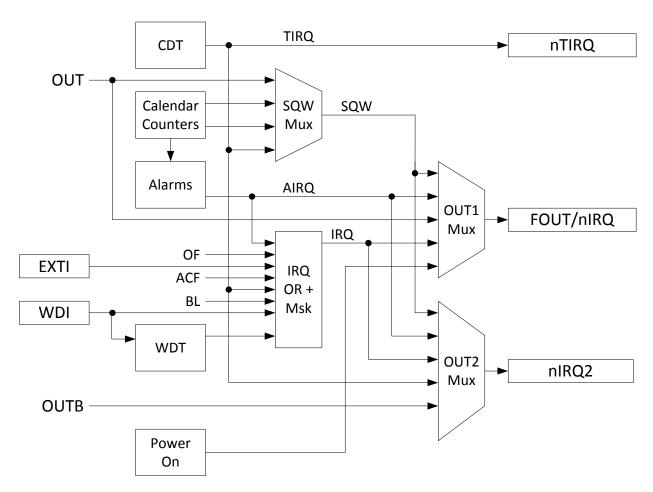

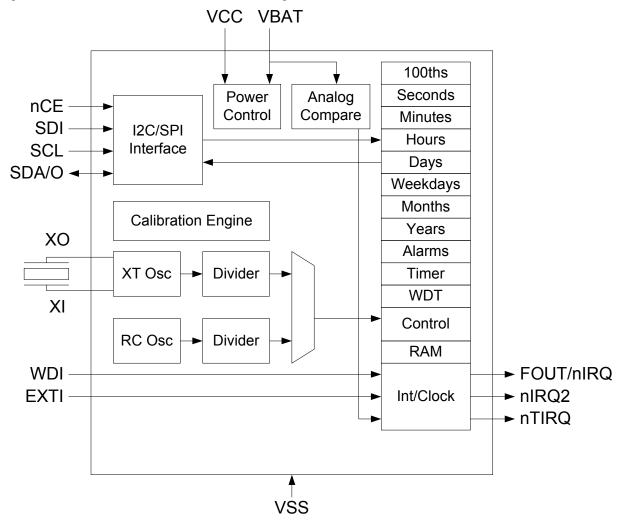

# 3. Digital Architecture Summary

Figure 2 illustrates the overall architecture of the pin inputs and outputs of the AM08X5.

Figure 2. Digital Architecture Summary

## 4. Electrical Specifications

## 4.1 Absolute Maximum Ratings

Table 4 lists the absolute maximum ratings.

**Table 4: Absolute Maximum Ratings**

| SYMBOL           | PARAMETER            | TEST CONDITIONS | MIN  | TYP | MAX                   | UNIT |

|------------------|----------------------|-----------------|------|-----|-----------------------|------|

| V <sub>CC</sub>  | System Power Voltage |                 | -0.3 |     | 3.8                   | V    |

| V <sub>BAT</sub> | Battery Voltage      |                 | -0.3 |     | 3.8                   | V    |

| VI               | Input voltage        | VCC Power state | -0.3 |     | V <sub>CC</sub> + 0.3 | V    |

**Table 4: Absolute Maximum Ratings**

| SYMBOL           | PARAMETER                    | TEST CONDITIONS                         | MIN  | TYP | MAX                    | UNIT |

|------------------|------------------------------|-----------------------------------------|------|-----|------------------------|------|

| V <sub>I</sub>   | Input voltage                | VBAT Power state                        | -0.3 |     | V <sub>BAT</sub> + 0.3 | V    |

| V <sub>O</sub>   | Output voltage               | VCC Power state                         | -0.3 |     | V <sub>CC</sub> + 0.3  | V    |

| V <sub>O</sub>   | Output voltage               | VBAT Power state                        | -0.3 |     | V <sub>BAT</sub> + 0.3 | V    |

| I <sub>I</sub>   | Input current                |                                         | -10  |     | 10                     | mA   |

| I <sub>O</sub>   | Output current               |                                         | -20  |     | 20                     | mA   |

| V <sub>ESD</sub> | ESD Voltage                  | CDM                                     |      |     | ±500                   | V    |

| *ESD             | LOD Vollage                  | НВМ                                     |      |     | ±4000                  | V    |

| I <sub>LU</sub>  | Latch-up Current             |                                         |      |     | 100                    | mA   |

| T <sub>STG</sub> | Storage Temperature          |                                         | -55  |     | 125                    | °C   |

| T <sub>OP</sub>  | Operating Temperature        |                                         | -40  |     | 85                     | °C   |

| T <sub>SLD</sub> | Lead temperature             | Hand soldering for 10 seconds           |      |     | 300                    | °C   |

| T <sub>REF</sub> | Reflow soldering temperature | Reflow profile per JEDEC J-<br>STD-020D |      |     | 260                    | °C   |

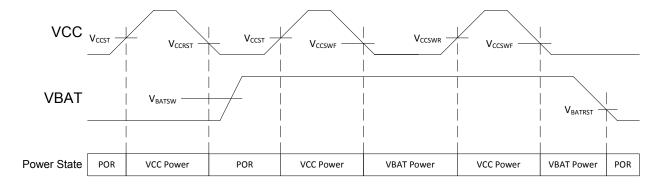

## 4.2 Power Supply Parameters

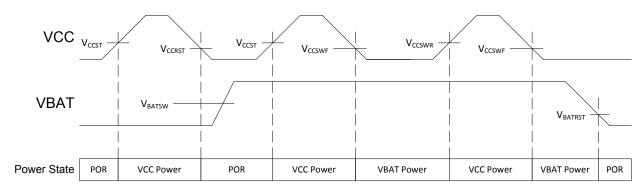

Figure 3 and Table 5 describe the power supply and switchover parameters. See Power Control and Switching for a detailed description of the operations.

Figure 3. Power Supply Switchover

For Table 5,  $T_A$  = -40 °C to 85 °C, TYP values at 25 °C.

**Table 5: Power Supply and Switchover Parameters**

| SYMBO<br>L      | PARAMETER            | PWR | TYPE   | POWER STATE | TEST<br>CONDITIONS                              | MIN | TYP | MAX | UNIT |

|-----------------|----------------------|-----|--------|-------------|-------------------------------------------------|-----|-----|-----|------|

| V <sub>CC</sub> | System Power Voltage | VCC | Static | VCC Power   | Clocks operating and RAM and registers retained | 1.5 |     | 3.6 | ٧    |

**Table 5: Power Supply and Switchover Parameters**

| SYMBO<br>L          | PARAMETER                                                    | PWR  | TYPE    | POWER STATE                  | TEST<br>CONDITIONS                                                | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------------------------------------------|------|---------|------------------------------|-------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>CCIO</sub>   | VCC I/O Interface<br>Voltage                                 | vcc  | Static  | VCC Power                    | I <sup>2</sup> C or SPI operation                                 | 1.5 |     | 3.6 | V    |

| V <sub>CCST</sub>   | VCC Start-up Voltage <sup>(1)</sup>                          | VCC  | Rising  | POR -> V <sub>CC</sub> Power |                                                                   | 1.6 |     |     | V    |

| V <sub>CCRST</sub>  | VCC Reset Voltage                                            | VCC  | Falling | VCC Power -> POR             | V <sub>BAT</sub> < V <sub>BAT,MIN</sub> or<br>no V <sub>BAT</sub> |     | 1.3 | 1.5 | ٧    |

| V <sub>CCSWR</sub>  | VCC Rising Switch-over<br>Threshold Voltage                  | VCC  | Rising  | VBAT Power -><br>VCC Power   | V <sub>BAT</sub> ≥ V <sub>BATRST</sub>                            |     | 1.6 | 1.7 | V    |

| V <sub>CCSWF</sub>  | VCC Falling Switch-over<br>Threshold Voltage                 | VCC  | Falling | VCC Power -><br>VBAT Power   | V <sub>BAT</sub> ≥ V <sub>BATSW,MIN</sub>                         | 1.2 | 1.5 |     | ٧    |

| V <sub>CCSWH</sub>  | VCC Switchover Threshold Hysteresis <sup>(2)</sup>           | VCC  | Hyst.   | VCC Power <-><br>VBAT Power  |                                                                   |     | 70  |     | mV   |

| V <sub>CCFS</sub>   | VCC Falling Slew Rate to switch to VBAT state <sup>(4)</sup> | VCC  | Falling | VCC Power -><br>VBAT Power   | V <sub>CC</sub> < V <sub>CCSW,MAX</sub>                           | 0.7 | 1.4 |     | V/ms |

| V <sub>BAT</sub>    | Battery Voltage                                              | VBAT | Static  | VBAT Power                   | Clocks operating<br>and RAM and reg-<br>isters retained           | 1.4 |     | 3.6 | ٧    |

| V <sub>BATSW</sub>  | Battery Switchover Voltage Range <sup>(5)</sup>              | VBAT | Static  | VCC Power -><br>VBAT Power   |                                                                   | 1.6 |     | 3.6 | V    |

| V <sub>BATRST</sub> | Falling Battery POR Voltage <sup>(7)</sup>                   | VBAT | Falling | VBAT Power -><br>POR         | V <sub>CC</sub> < V <sub>CCSWF</sub>                              |     | 1.1 | 1.4 | V    |

| $V_{BMRG}$          | V <sub>BAT</sub> Margin above V <sub>CC</sub> <sup>(3)</sup> | VBAT | Static  | V <sub>BAT</sub> Power       |                                                                   | 200 |     |     | mV   |

| V <sub>BATESR</sub> | V <sub>BAT</sub> supply series resistance <sup>(6)</sup>     | VBAT | Static  | V <sub>BAT</sub> Power       |                                                                   | 1.0 | 1.5 |     | kΩ   |

$<sup>^{(1)}</sup>V_{CC}$  must be above  $V_{CCST}$  to exit the POR state, independent of the  $V_{BAT}$  voltage.

## 4.3 Operating Parameters

Table 6 lists the operating parameters.

For Table 6,  $T_A$  = -40 °C to 85 °C, TYP values at 25 °C.

$<sup>^{(2)}\</sup>mbox{Difference}$  between  $\mbox{V}_{\mbox{CCSWR}}$  and  $\mbox{V}_{\mbox{CCSWF}}.$

$<sup>^{(3)}</sup>V_{BAT}$  must be higher than  $V_{CC}$  by at least this voltage to ensure the AM08X5 remains in the VBAT Power state.

<sup>&</sup>lt;sup>(4)</sup>Maximum VCC falling slew rate to guarantee correct switchover to VBAT Power state. There is no V<sub>CC</sub> falling slew rate requirement if switching to the VBAT power source is not required.

$<sup>^{(5)}</sup>V_{BAT}$  voltage to guarantee correct transition to VBAT Power state when  $V_{CC}$  falls.

<sup>&</sup>lt;sup>(6)</sup>Total series resistance of the power source attached to the VBAT pin. The optimal value is 1.5kΩ, which may require an external resistor. VBAT power source ESR + external resistor value = 1.5kΩ.

<sup>(7)</sup> V<sub>BATRST</sub> is also the static voltage required on V<sub>BAT</sub> for register data retention.

### **Table 6: Operating Parameters**

| SYMBOL             | PARAMETER                                      | TEST<br>CONDITIONS                                             | <b>v</b> <sub>cc</sub> | MIN                 | TYP  | MAX                 | UNIT |      |

|--------------------|------------------------------------------------|----------------------------------------------------------------|------------------------|---------------------|------|---------------------|------|------|

| V <sub>T+</sub>    | Positive-going Input Thresh-                   |                                                                | 3.0V                   |                     | 1.5  | 2.0                 | V    |      |

| V T+               | old Voltage                                    |                                                                | 1.8V                   |                     | 1.1  | 1.25                | v    |      |

| V <sub>T-</sub>    | Negative-going Input Thresh-                   |                                                                | 3.0V                   | 0.8                 | 0.9  |                     | V    |      |

| ▼T-                | old Voltage                                    |                                                                | 1.8V                   | 0.5                 | 0.6  |                     | v    |      |

| I <sub>ILEAK</sub> | Input leakage current                          |                                                                | 3.0V                   |                     | 0.02 | 80                  | nA   |      |

| C <sub>I</sub>     | Input capacitance                              |                                                                |                        |                     | 3    |                     | pF   |      |

| V <sub>OH</sub>    | High level output voltage on push-pull outputs |                                                                | 1.7V – 3.6V            | 0.8•V <sub>CC</sub> |      |                     | V    |      |

| V <sub>OL</sub>    | Low level output voltage                       |                                                                | 1.7V – 3.6V            |                     |      | 0.2•V <sub>CC</sub> | V    |      |

|                    |                                                |                                                                | 1.7V                   | -2                  | -3.8 |                     |      |      |

| I <sub>OH</sub>    | High level output current on                   | V <sub>OH</sub> = 0.8•V <sub>CC</sub>                          | 1.8V                   | -3                  | -4.3 |                     | mA   |      |

| 'ОН                | push-pull outputs                              | AOH - 0.00 ACC                                                 | 3.0V                   | -7                  | -11  |                     | IIIA |      |

|                    |                                                |                                                                | 3.6V                   | -8.8                | -15  |                     |      |      |

|                    |                                                |                                                                | 1.7V                   | 3.3                 | 5.9  |                     |      |      |

| la                 | Low lovel output current                       | V <sub>OI</sub> = 0.2•V <sub>CC</sub>                          | 1.8V                   | 6.1                 | 6.9  |                     | mA   |      |

| l <sub>OL</sub>    | Low level output current                       | Low level output current V <sub>OL</sub> = 0.2•V <sub>CC</sub> | VOL - 0.2 VCC          | 3.0V                | 17   | 19                  |      | IIIA |

|                    |                                                |                                                                | 3.6V                   | 18                  | 20   |                     |      |      |

| I <sub>OLEAK</sub> | Output leakage current                         |                                                                | 1.7V – 3.6V            |                     | 0.02 | 80                  | nA   |      |

#### 4.4 Oscillator Parameters

Table 7 lists the oscillator parameters.

For Table 7,  $T_A$  = -40 °C to 85 °C unless otherwise indicated.  $V_{CC}$  = 1.7 to 3.6V, TYP values at 25 °C and 3.0V.

**Table 7: Oscillator Parameters**

| SYMBOL           | PARAMETER                                                 | TEST CONDITIONS                                  | MIN | TYP    | MAX | UNIT |

|------------------|-----------------------------------------------------------|--------------------------------------------------|-----|--------|-----|------|

| F <sub>XT</sub>  | XI and XO pin Crystal Frequency                           |                                                  |     | 32.768 |     | kHz  |

| F <sub>OF</sub>  | XT Oscillator failure detection frequency                 |                                                  |     | 8      |     | kHz  |

| C <sub>INX</sub> | Internal XI and XO pin capacitance                        |                                                  |     | 1      |     | pF   |

| C <sub>EX</sub>  | External XI and XO pin PCB capacitance                    |                                                  |     | 1      |     | pF   |

| OA <sub>XT</sub> | XT Oscillation Allowance                                  | At 25°C using a 32.768 kHz crystal               | 270 | 320    |     | kΩ   |

| F <sub>RCC</sub> | Calibrated RC Oscillator Frequency <sup>(1)</sup>         | Factory Calibrated at 25°C,<br>VCC = 2.8V        |     | 128    |     | Hz   |

| F <sub>RCU</sub> | Uncalibrated RC Oscillator Frequency                      | Calibration Disabled (OFF-<br>SETR = 0)          | 89  | 122    | 220 | Hz   |

| JRCCC            | RC Oscillator cycle-to-cycle                              | Calibration Disabled (OFF-<br>SETR = 0) – 128 Hz |     | 2000   |     | ppm  |

| RCCC             | jitter                                                    | Calibration Disabled (OFF-SETR = 0) – 1 Hz       |     | 500    |     | ррш  |

| A <sub>XT</sub>  | XT mode digital calibration accuracy <sup>(1)</sup>       | Calibrated at an initial temperature and voltage | -2  |        | 2   | ppm  |

|                  |                                                           | 24 hour run time                                 |     | 35     |     |      |

| Δ                | Autocalibration mode timing accuracy, 512 second period,  | 1 week run time                                  |     | 20     |     | nnm  |

| A <sub>AC</sub>  | $T_A = -10^{\circ}C \text{ to } 60^{\circ}C^{(1)}$        | 1 month run time                                 |     | 10     |     | ppm  |

|                  |                                                           | 1 year run time                                  |     | 3      |     |      |

| T <sub>AC</sub>  | Autocalibration mode operating temperature <sup>(2)</sup> |                                                  | -10 |        | 60  | °C   |

<sup>(1)</sup> Timing accuracy is specified at 25°C after digital calibration of the internal RC oscillator and 32.768 kHz crystal. A typical 32.768 kHz tuning fork crystal has a negative temperature coefficient with a parabolic frequency deviation, which due to the crystal alone can result in a change of up to 150 ppm across the entire operating temperature range of -40°C to 85°C in XT mode. Autocalibration mode timing accuracy is specified relative to XT mode timing accuracy from -10°C to 60°C.

<sup>(2)</sup> Outside of this temperature range, the RC oscillator frequency change due to temperature may be outside of the allowable RC digital calibration range (+/-12%) for autocalibration mode. If this happens, an autocalibration failure will occur and the ACF interrupt flag is set. The AM08X5 should be switched to use the XT oscillator as its clock source. Please see the Autocalibration Fail section for more details.

Figure 4 shows the typical calibrated RC oscillator frequency variation vs. temperature. RC oscillator calibrated at 2.8V, 25°C.

Figure 4. Calibrated RC Oscillator Typical Frequency Variation vs. Temperature

Figure 5 shows the typical uncalibrated RC oscillator frequency variation vs. temperature.

Figure 5. Uncalibrated RC Oscillator Typical Frequency Variation vs. Temperature

## 4.5 V<sub>CC</sub> Supply Current

Table 8 lists the current supplied into the VCC power input under various conditions.

For Table 8,  $T_A$  = -40 °C to 85 °C, VBAT = 0 V to 3.6 V TYP values at 25 °C, MAX values at 85 °C, VCC Power state

**Table 8: V<sub>CC</sub> Supply Current**

| SYMBOL                 | PARAMETER                                              | TEST CONDITIONS                                                                          | vcc  | MIN | TYP | MAX | UNIT |

|------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------|------|-----|-----|-----|------|

| I <sub>VCC:I2C</sub>   | V <sub>CC</sub> supply current during I <sup>2</sup> C | 400kHz bus speed, 2.2k pull-up                                                           | 3.0V |     | 6   | 10  | μA   |

| . VCC.12C              | burst read/write                                       | resistors on SCL/SDA <sup>(1)</sup>                                                      | 1.8V |     | 1.5 | 3   | μπ   |

| I <sub>VCC:SPIW</sub>  | V <sub>CC</sub> supply current during SPI              | 2 MHz bus speed (2)                                                                      | 3.0V |     | 8   | 12  | μA   |

| ·VCC:SPIW              | burst write                                            | 2 IVII IZ bus speed V                                                                    | 1.8V |     | 4   | 6   | μ, τ |

| I <sub>VCC:SPIR</sub>  | V <sub>CC</sub> supply current during SPI              | 2 MHz bus speed (2)                                                                      | 3.0V |     | 23  | 37  | μA   |

| VCC:SPIR               | burst read                                             | Z IVITIZ bus speed V                                                                     | 1.8V |     | 13  | 21  | μΑ   |

| I <sub>VCC:XT</sub>    | V <sub>CC</sub> supply current in XT oscil-            | Time keeping mode with XT                                                                | 3.0V |     | 55  | 330 | nA   |

| WCC:X1                 | lator mode                                             | oscillator running <sup>(3)</sup>                                                        | 1.8V |     | 51  | 290 | 101  |

|                        | V <sub>CC</sub> supply current in RC oscil-            | Time keeping mode with only                                                              | 3.0V |     | 14  | 220 | nA   |

| I <sub>VCC:RC</sub>    | lator mode                                             | the RC oscillator running (XT oscillator is off) <sup>(3)</sup>                          | 1.8V |     | 11  | 170 |      |

|                        | Average V <sub>CC</sub> supply current in              | Time keeping mode with only                                                              | 3.0V |     | 22  | 235 |      |

| I <sub>VCC:ACAL</sub>  | Autocalibrated RC oscillator mode                      | RC oscillator running and Auto-<br>calibration enabled. ACP = 512 seconds <sup>(3)</sup> | 1.8V |     | 18  | 190 | nA   |

|                        | Additional V <sub>CC</sub> supply current              | Time keeping mode with XT                                                                | 3.0V |     | 3.6 | 8   |      |

| I <sub>VCC:CK32</sub>  | with CLKOUT at 32.786 kHz                              | oscillator running, 32.786 kHz square wave on CLKOUT <sup>(4)</sup>                      | 1.8V |     | 2.2 | 5   | μΑ   |

| I <sub>VCC:CK128</sub> | Additional V <sub>CC</sub> supply current              | All time keeping modes, 128 Hz                                                           | 3.0V |     | 7   | 35  | nA   |

| -VCC.CN126             | with CLKOUT at 128 Hz                                  | square wave on CLKOUT <sup>(4)</sup>                                                     | 1.8V |     | 2.5 | 20  | 101  |

<sup>(1)</sup> Excluding external peripherals and pull-up resistor current. All other inputs (besides SDA and SCL) are at 0V or V<sub>CC</sub>. AM0805 only. Test conditions: Continuous burst read/write, 0x55 data pattern, 25 μs between each data byte, 20 pF load on each bus pin.

$<sup>^{(2)}</sup>$  Excluding external peripheral current. All other inputs (besides SDI, nCE and SCL) are at 0V or V<sub>CC</sub>. AM0815 only. Test conditions: Continuous burst write, 0x55 data pattern, 25  $\mu$ s between each data byte, 20 pF load on each bus pin.

$<sup>^{(3)}</sup>$ All inputs and outputs are at 0 V or  $V_{CC}$ .

$<sup>^{(4)}</sup>$ All inputs and outputs except CLKOUT are at 0 V or V<sub>CC</sub>. 15 pF capacitive load on CLKOUT.

Figure 6 shows the typical VCC power state operating current vs. temperature in XT mode.

Figure 6. Typical VCC Current vs. Temperature in XT Mode

Figure 7 shows the typical VCC power state operating current vs. temperature in RC mode.

Figure 7. Typical VCC Current vs. Temperature in RC Mode

Figure 8 shows the typical VCC power state operating current vs. temperature in RC Autocalibration mode.

Figure 8. Typical VCC Current vs. Temperature in RC Autocalibration Mode

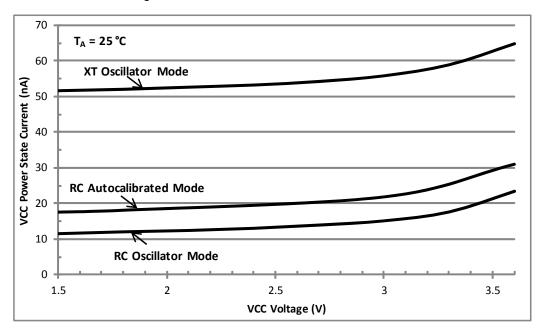

Figure 9 shows the typical VCC power state operating current vs. voltage for XT Oscillator and RC Oscillator modes and the average current in RC Autocalibrated mode.

Figure 9. Typical VCC Current vs. Voltage, Different Modes of Operation

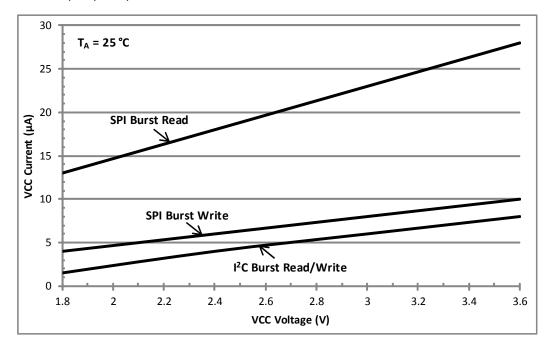

Figure 10 shows the typical VCC power state operating current during continuous I $^2$ C and SPI burst read and write activity. Test conditions:  $T_A$  = 25 °C, 0x55 data pattern, 25  $\mu$ s between each data byte, 20 pF load on each bus pin, pull-up resistor current not included.

Figure 10. Typical VCC Current vs. Voltage, I<sup>2</sup>C and SPI Burst Read/Write

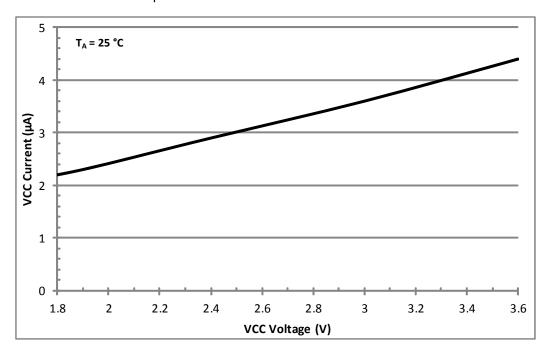

Figure 11 shows the typical VCC power state operating current with a 32.768 kHz clock output on the CLKOUT pin. Test conditions:  $T_A = 25$  °C, All inputs and outputs except CLKOUT are at 0 V or VCC. 15 pF capacitive load on the CLKOUT pin.

Figure 11. Typical VCC Current vs. Voltage, 32.768 kHz Clock Output

## 4.6 VBAT Supply Current

Table 9 lists the current supplied into the VBAT power input under various conditions.

For Table 9,  $T_A$  = -40 °C to 85 °C, TYP values at 25 °C, MAX values at 85 °C,  $V_{BAT}$  Power state.

Table 9: V<sub>BAT</sub> Supply Current

| SYMBOL                  | PARAMETER                                                                   | TEST CONDITIONS                                                                            | <b>v</b> <sub>cc</sub> | V <sub>BAT</sub> | MIN | TYP | MAX | UNIT |

|-------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------------------------|------------------|-----|-----|-----|------|

| I <sub>VBAT:XT</sub>    | VBAT supply current in                                                      | Time keeping mode with                                                                     | < V <sub>CCSWF</sub>   | 3.0V             |     | 56  | 330 | nA   |

| ·VBAI.XI                | XT oscillator mode                                                          | XT oscillator running <sup>(1)</sup>                                                       | * CC3WF                | 1.8V             |     | 52  | 290 |      |

|                         | VBAT supply current in                                                      | Time keeping mode with                                                                     | 41/                    | 3.0V             |     | 16  | 220 |      |

| IVBAT:RC                | RC oscillator mode                                                          | only the RC oscillator running (XT oscillator is off) <sup>(1)</sup>                       | < V <sub>CCSWF</sub>   | 1.8V             |     | 12  | 170 | nA   |

|                         | Average VBAT supply                                                         | Time keeping mode with                                                                     |                        | 3.0V             |     | 24  | 235 |      |

| I <sub>VBAT:ACAL</sub>  | current in Autocalibrated RC oscillator mode                                | the RC oscillator running.<br>Autocalibration enabled.<br>ACP = 512 seconds <sup>(1)</sup> | < V <sub>CCSWF</sub>   | 1.8V             |     | 20  | 190 | nA   |

| luna Turon              | VBAT supply current in                                                      | V <sub>CC</sub> powered mode <sup>(1)</sup>                                                | 1.7 - 3.6 V            | 3.0V             | -5  | 0.6 | 20  | nA   |

| IVBAT:VCC               | VCC powered mode                                                            | ACC boweled illoge.                                                                        | 1.7 - 3.0 V            | 1.8V             | -10 | 0.5 | 16  | ПΛ   |

| <sup>(1)</sup> Test coi | (1) Test conditions: All inputs and outputs are at 0 V or V <sub>CC</sub> . |                                                                                            |                        |                  |     |     |     |      |

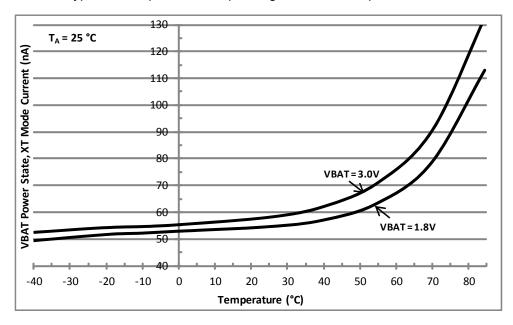

Figure 12 shows the typical VBAT power state operating current vs. temperature in XT mode.

Figure 12. Typical VBAT Current vs. Temperature in XT Mode

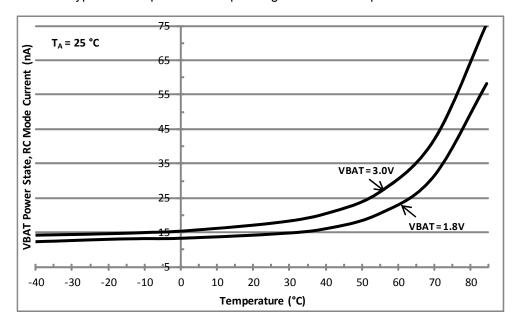

Figure 13 shows the typical VBAT power state operating current vs. temperature in RC mode.

Figure 13. Typical VBAT Current vs. Temperature in RC Mode

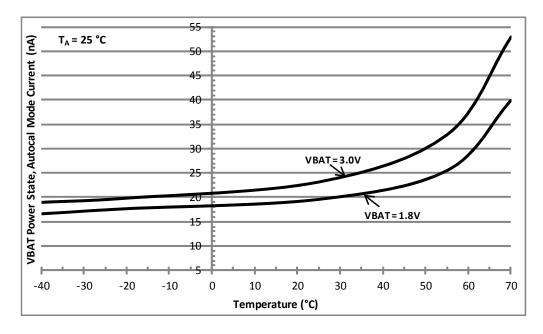

Figure 14 shows the typical VBAT power state operating current vs. temperature in RC Autocalibration mode.

Figure 14. Typical VBAT Current vs. Temperature in RC Autocalibration Mode

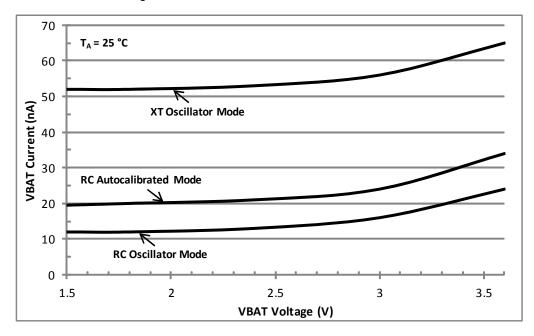

Figure 15 shows the typical VBAT power state operating current vs. voltage for XT Oscillator and RC Oscillator modes and the average current in RC Autocalibrated mode, VCC = 0 V.

Figure 15. Typical VBAT Current vs. Voltage, Different Modes of Operation

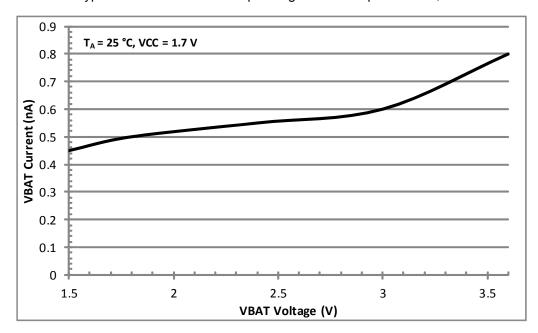

Figure 16 shows the typical VBAT current when operating in the VCC power state, VCC = 1.7 V.

Figure 16. Typical VBAT Current vs. Voltage in VCC Power State

#### 4.7 BREF Electrical Characteristics

Table 10 lists the parameters of the VBAT voltage thresholds. BREF values other than those listed in the table are not supported.

For Table 10,  $T_A$  = -20 °C to 70 °C, TYP values at 25 °C, VCC = 1.7 to 3.6V.

**Table 10: BREF Parameters**

| SYMBOL           | PARAMETER                                                      | BREF       | MIN | TYP | MAX | UNIT |

|------------------|----------------------------------------------------------------|------------|-----|-----|-----|------|

|                  |                                                                | 0111       | 2.3 | 2.5 | 3.3 |      |

| $V_{BRF}$        | VBAT falling threshold                                         | 1011       | 1.9 | 2.1 | 2.8 | V    |

| *BKF             |                                                                | 1101       | 1.6 | 1.8 | 2.5 | v    |

|                  |                                                                | 1111       |     | 1.4 |     |      |

|                  |                                                                | 0111       | 2.6 | 3.0 | 3.4 |      |

| V <sub>BRR</sub> | VBAT rising threshold                                          | 1011       | 2.1 | 2.5 | 2.9 | V    |