PRELIMINARY

CYW20745

# ROM-Based Single Microphone Headset IC With Voice Command Recognition

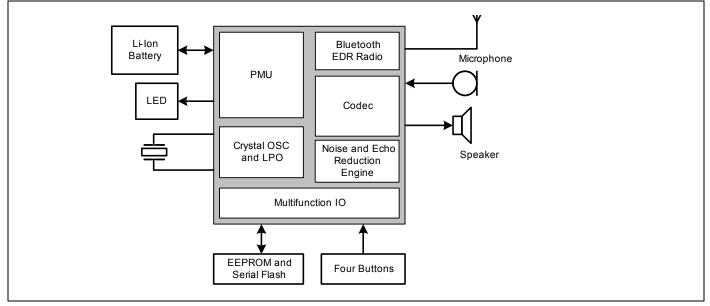

Cypress CYW20745 is a Bluetooth 3.0 monolithic IC solution for single microphone mono headset applications with radio, baseband, application ROM, power management, mono single microphone codec, and many other components typically required for low-cost headset designs, making it ideal for low-cost, footprint-challenged headset designs. This device is the world's first ROM-based design to support voice command recognition and multilanguage voice prompts without needing to add large expensive memory in the external BOM.

The CYW20745 also delivers differentiating features, including enhanced audio quality and reduced charging times, A2DP, and multipoint connections, through the integration of various noise suppression technologies, circuitry, and application profiles. It is a ROM-based noise and echo reduction headset, enabling a revolutionary reduction in the bill of materials (BOM) for high-end, midrange, and low-cost mono headsets.

The CYW20745 is designed for enabling features and audio quality that are usually available only for high-end products, but at a fraction of the cost of existing solutions.

The CYW20745 supports the Bluetooth 3.0 standard, adding enhanced power control, simple and secure pairing, and enhanced inquiry response as value-added features for Bluetooth headsets.

All major functional blocks required for a mono headset, including PMU, charger, and audio codec are integrated into a single package providing low system cost, ease of implementation, and high product yields.

This device uses 65 nm process that provides significant power reduction compared to older processes.

# **Cypress Part Numbering Scheme**

Cypress is converting the acquired IoT part numbers from Broadcom to the Cypress part numbering scheme. Due to this conversion, there is no change in form, fit, or function as a result of offering the device with Cypress part number marking. The table provides Cypress ordering part number that matches an existing IoT part number.

#### Table 1. Mapping Table for Part Number between Broadcom and Cypress

| Broadcom Part Number | Cypress Part Number |

|----------------------|---------------------|

| BCM20745             | CYW20745            |

| BCM20745A0KMLGT      | CYW20745A0KMLGT     |

| BCM20745A0KMLG       | CYW20745A0KMLG      |

| BCM20745A0KFBGT      | CYW20745A0KFBGT     |

| BCM20745A0KFBG       | CYW20745A0KFBG      |

### Acronyms and Abbreviations

In most cases, acronyms and abbreviations are defined on first use.

For a comprehensive list of acronyms and other terms used in Cypress documents, go to: http://www.cypress.com/glossary

# Applications

■ The CYW20745 is fully optimized for mono headset products.

198 Champion Court

# Features

- Single-chip Bluetooth 3.0 transceiver supporting Bluetooth 2.1

+ Enhanced Data Rate (EDR) and Bluetooth 2.0, 1.2, and 1.1

backward compatibility

- Best-in-class Bluetooth radio with 8 dBm transmit power and -91 dBm receive sensitivity

- Support for side tone and digital microphones

- Supports microphone and speaker equalization

- High-performance ARM Cortex<sup>™</sup>-M3 processor

- On-chip SRAM and ROM

- Extensive configuration tool for application differentiation and audio path tuning

- Integrated SmartAudio® speech enhancement algorithms

Noise suppression

- Echo suppression

- □ Wind-noise suppression

- □ Packet-loss concealment

- □ Bit-error concealment

- □ Speech-intelligibility enhancement

- □ Automatic gain control (AGC) and automatic volume control (AVC)

- UART and UART over USB adapter for test and configuration

- Switching regulator, battery charger, and power management unit

- Supports fast charging, power dissipation monitoring, and optional charger voltage regulation

- High quality 8 kHz and 16 kHz audio codec with a single microphone interface

- Low power operation

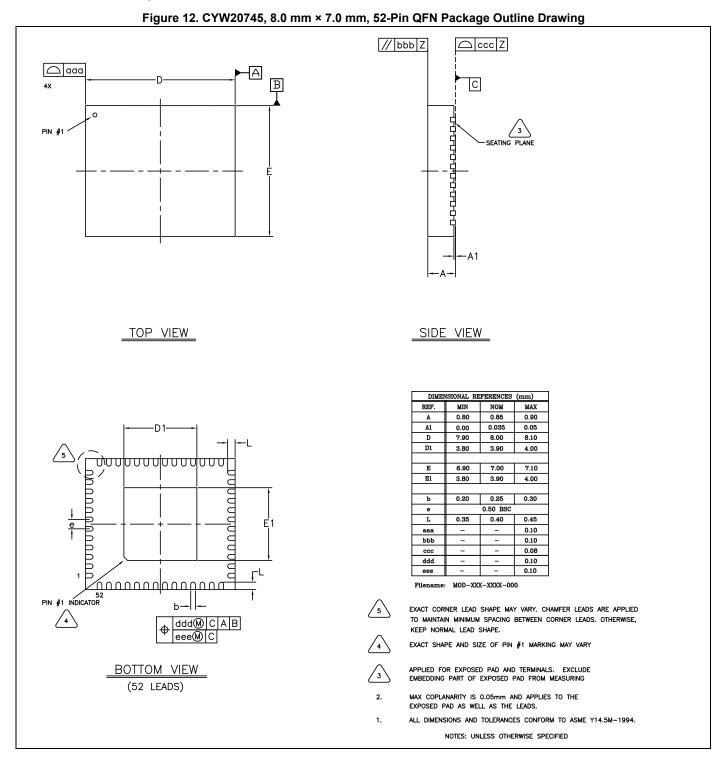

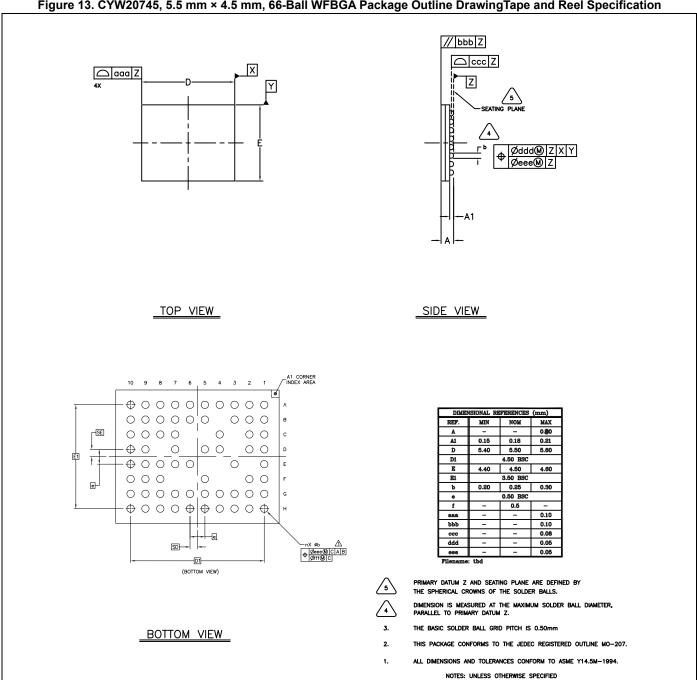

- 5.5 mm × 4.5 mm, 66-ball WFBGA package with a 0.5 mm pitch and a 7 mm x 8 mm, 52-pin QFN package with a 0.5 mm pitch

- Pin-to-pin compatible with the CYW20740/CYW20741/ CYW20742

- Full-featured and configurable mono headset application firmware built on Cypress's Bluetooth for embedded (BTE) audio stack

- Infinite Shelf Life Extension support

- Multilanguage voice prompt

- Advanced multipoint

- Pairing enhancements

- A2DP over mono

- Voice command recognition

### Figure 1. CYW20745 Functional Block Diagram

# **IoT Resources**

Cypress provides a wealth of data at http://www.cypress.com/internet-things-iot to help you to select the right IoT device for your design, and quickly and effectively integrate the device into your design. Cypress provides customer access to a wide range of information, including technical documentation, schematic diagrams, product bill of materials, PCB layout information, and software updates. Customers can acquire technical documentation and software from the Cypress Support Community website (http:// community.cypress.com/).

# Contents

| 1. Overview                               | 4    |

|-------------------------------------------|------|

| 1.1 Features                              |      |

| 1.2 Configuration Parameters              | 5    |

| 1.3 Detailed Block Diagram                |      |

| 2. Bluetooth Transceiver                  | 7    |

| 2.1 EDR Radio Transmitter Path            | 7    |

| 2.2 EDR Radio Receiver Path               | 8    |

| 2.3 EDR Radio Local Oscillator Generation | 8    |

| 2.4 EDR Radio Calibration                 | 8    |

| 2.5 Bluetooth Baseband Core               | 8    |

| 3. CPU Subsystem                          | 9    |

| 3.1 Cortex-M3™                            |      |

| 3.2 On-Chip Memories                      | 9    |

| 3.3 Watchdog Timer                        | 9    |

| 3.4 General-Purpose Timer                 |      |

| 3.5 ARM® JTAG                             |      |

| 3.6 External Reset                        |      |

| 4. Power Management Unit                  |      |

| 4.1 Switching Regulator                   | . 11 |

| 4.2 LDO Regulators                        |      |

| 4.3 Battery Charger                       |      |

| 4.4 LED Drivers                           | 13   |

| 5. Peripherals                            |      |

| 5.1 UART Interface                        |      |

| 5.2 BSC Interface                         |      |

| 5.3 SPI Interface                         |      |

| 5.4 GPIO                                  | 15   |

|                                           |      |

| 6. Audio                                   | 16 |

|--------------------------------------------|----|

| 6.1 Codec                                  | 16 |

| 6.2 Speech Codecs                          | 17 |

| 6.3 A2DP Codec                             | 17 |

| 6.4 Digital Microphone Support             | 17 |

| 7. Frequency References                    |    |

| 7.1 Crystal Interface and Clock Generation | 18 |

| 7.2 Low-Power Oscillator                   |    |

| 8. Operation                               |    |

| 8.1 CYW20745 Modes of Operation            | 19 |

| 9. Pin Assignments                         | 20 |

| 10. Specifications                         | 26 |

| 10.1 Environmental Specifications          | 26 |

| 10.2 Maximum Rating Specifications         | 26 |

| 10.3 PMU Specifications                    | 26 |

| 10.4 General I/O                           | 28 |

| 10.5 RF Specifications                     | 29 |

| 10.6 Audio Specifications                  | 33 |

| 10.7 Timing and AC Specifications          | 35 |

| 10.8 Power Consumption                     | 37 |

| 11. Mechanical Specification               | 38 |

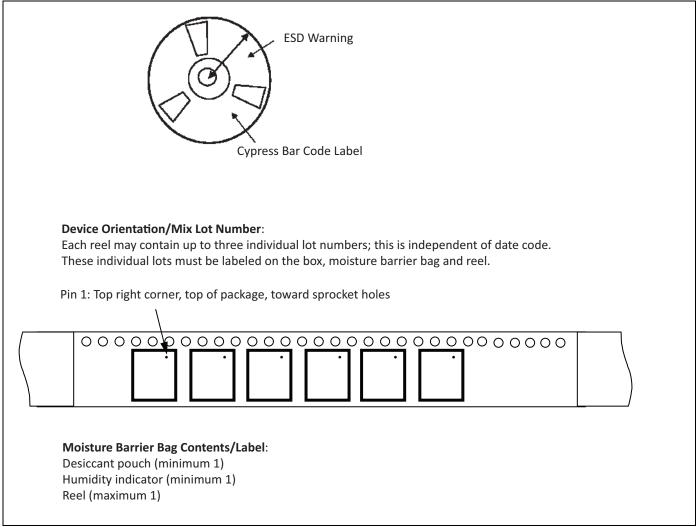

| 11.1 Tape and Reel Specification           | 40 |

| 12. Ordering Information                   | 41 |

| 12.1 References                            | 41 |

| Document History                           | 42 |

# 1. Overview

The Cypress CYW20745 is a monolithic, single-chip, Bluetooth 3.0-compliant, stand-alone baseband processor with an integrated 2.4 GHz transceiver. It is a ROM-based, single microphone, mono headset IC with noise and echo reduction. The CYW20745 features the highest level of integration and eliminates all critical external components, thereby minimizing the footprint and reducing the system cost associated with implementing a Bluetooth audio solution.

### 1.1 Features

The features supported by the CYW20745 are listed below:

- Fully supports Bluetooth 3.0 and 2.1+EDR features and is Bluetooth 2.0, 1.2, and 1.1 backward compatible. Feature support includes the following:

- Bluetooth Enhanced Data Rate (EDR)

- □ Adaptive Frequency Hopping (AFH)

- Quality of Service (QoS)

- ⊐ eSCO

- Fast connect

- Enhanced power control

- Integrated SmartAudio® speech enhancement algorithms which include:

- Noise suppression

- □ Echo suppression

- Wind-noise suppression

- Packet-loss concealment

- Bit-error concealment

- A speech-intelligibility enhancement

- Automatic gain control and automatic volume control

- □ An echo cancellation enhancement for a carkit

- Best in class Bluetooth radio with 8 dBm transmit power and -91 dBm receive sensitivity

- A2DP over mono

- Voice command recognition

- Support for side tone and digital microphones

- Supports microphone and speaker equalization

- High-performance ARM Cortex-M3 processor

- On-chip SRAM and ROM

- Extensive configuration tool for application differentiation and audio path tuning

- UART and UART over USB adapter for test and configuration

- Maximum UART baud rates of 1.5 Mbps

- Built-in transmit/receive switch and balun

- High-quality 8 kHz and 16 kHz audio codec with a single microphone interface

- Switching regulator, battery charger, and power management unit

- Automatic power saving modes

- Built-in low power oscillator to support deep sleep

- Supports fast charging, power dissipation control, and optional charger voltage regulation

- Built-in Low-Dropout (LDO) regulators

- Independent software-controlled regulator shutdown

- 5.5 mm × 4.5 mm, 66-ball WFBGA package with a 0.5 mm pitch, and a 7 mm × 8 mm, 52-pin QFN package with a 0.5 mm pitch

- Full-featured and configurable mono headset application firmware built on the Cypress BTE audio stack including application enhancements like multilanguage voice prompts, advance multipoint, and pairing enhancements

### **1.2 Configuration Parameters**

The following features can be configured using a simple GUI-based configuration tool. These features are programmed into the EEPROM using a PC attached to the CYW20745 UART port.

- Power Management Unit (PMU) parameters

- LED states (duty cycle, events, brightness, etc.)

- Speech path gain settings

- Event-based tone generation

- $\ensuremath{\square}$  Ring tone selections

- Events definition

- General-Purpose Input/Output (GPIO) mask

- Button functionality (timing and sequence definition)

- Bluetooth parameters

- Pairing timeout

- □ Hands-Free Profile (HFP) features

- Network time

- Auto reconnect

- Power saving modes

- Power on/off timer

- Automatic switch-off timer

- Friendly device name

- Bluetooth Device (BD) address

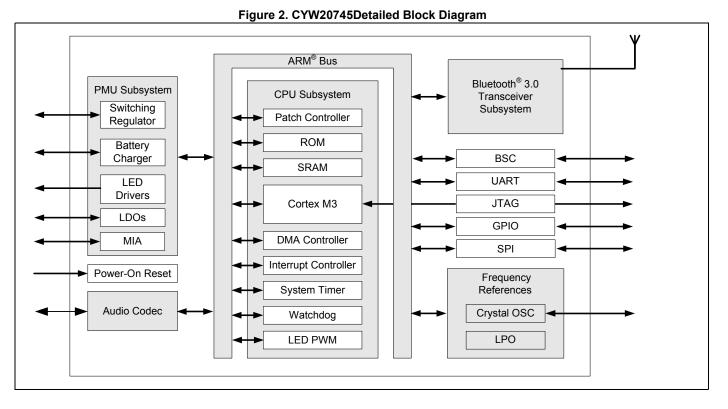

### 1.3 Detailed Block Diagram

Figure 2 illustrates the major internal components of the CYW20745.

Major subsystems are described in the following sections:

- Section 2.: "Bluetooth Transceiver," on page 7

- Section 3.: "CPU Subsystem," on page 9

- Section 4.: "Power Management Unit," on page 11

- Section 5.: "Peripherals," on page 14

- Section 6.: "Audio," on page 16

- Section 7.: "Frequency References," on page 18

CYW20745 modes of operation are described in Section 8.: "Operation," on page 19.

# 2. Bluetooth Transceiver

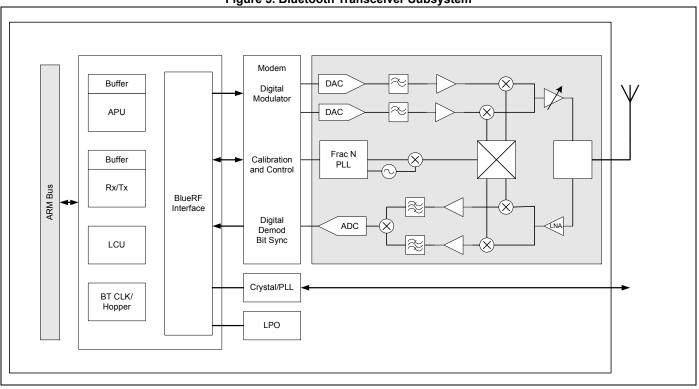

The CYW20745 has an integrated radio transceiver that has been optimized for use in 2.4 GHz Bluetooth wireless systems. It has been designed to provide low power, low cost, and robust communications for applications operating in the globally available 2.4 GHz unlicensed Industrial, Scientific, and Medical (ISM) band. It is fully compliant with the Bluetooth Radio Specification and EDR specification, and meets or exceeds the requirements to provide the highest communication link QoS. Figure 3 shows the individual components within the Bluetooth transceiver.

#### 2.1 EDR Radio Transmitter Path

The CYW20745 features a fully integrated zero-IF transmitter. The baseband transmits GFSK data that is digitally modulated in the modem block, and then upconverts the data to the 2.4 GHz ISM band in the transmitter path. The transmitter path consists of signal filters, I/Q upconverters, output Power Amplifiers (PAs), and RF filters. It also incorporates  $\pi$ /4-DQPSK modulation for 2 Mbps and 8-DPSK modulation for 3 Mbps to support EDR.

#### 2.1.1 Digital Modulator

The digital modulator performs the data modulation and filtering required for the GFSK,  $\pi$ /4-DQPSK, and 8-DPSK signals. The fully digital modulator minimizes any frequency drift or anomalies in the modulation characteristics of the transmitted signal and is much more stable than direct VCO modulation schemes.

#### 2.1.2 Power Amplifier

The fully integrated PA is configurable for Class 2 operation as well as Class 1 operation with higher supply voltage to the power amplifier, using a highly linearized, temperature-compensated design. This feature provides the user with greater flexibility and options in the type of front-end matching and filtering to use with the CYW20745.

### 2.2 EDR Radio Receiver Path

The receiver path uses a low-IF architecture to downconvert the received signal for demodulation in the digital demodulator and bit synchronizer. The receiver path provides a high degree of linearity, an extended dynamic range, and high-order on-chip channel filtering to ensure reliable operation in the noisy 2.4 GHz ISM band. The front-end topology with built-in out-of-band attenuation enables the CYW20745 to be used in most applications with no off-chip filtering.

#### 2.2.1 Digital Demodulator and Bit Synchronizer

The digital demodulator and bit synchronizer take the low-IF received signal and perform an optimal frequency tracking and bit synchronization algorithm.

#### 2.2.2 Receiver Signal Strength Indicator

The radio portion of the CYW20745 provides a Received Signal Strength Indication (RSSI) signal to the baseband so that the controller can participate in a Bluetooth power-controlled link. This occurs by providing a metric of its own receiver signal strength to determine whether the transmitter should increase or decrease its output power.

#### 2.3 EDR Radio Local Oscillator Generation

Local oscillator (LO) generation provides fast frequency hopping (1600 hops/second) across the 79 maximum available channels. The LO generation subblock employs an architecture for high immunity to LO pulling during PA operation. The CYW20745 uses an internal RF and IF loop filter.

#### 2.4 EDR Radio Calibration

The CYW20745 radio transceiver features an automated calibration scheme that is fully self contained in the radio. No user intervention is required during normal operation or during manufacturing, to provide for optimal performance. Calibration optimizes all major blocks in the radio to within 2 percent of optimal performance. The calibration process accounts for process variation and temperature variation. Calibration occurs transparently during normal operation and during the setting time of hops. The transceiver then calibrates temperature variations as the device cools and heats during normal operation within its environment.

#### 2.5 Bluetooth Baseband Core

The Bluetooth Baseband Core (BBC) implements all of the time-critical functions required for high-performance Bluetooth operations. The BBC manages the buffering, segmentation, and routing of data for all connections. It also buffers data that passes through it, handles data flow control, schedules SCO/ACL TX/RX transactions, monitors Bluetooth slot usage, optimally segments and packages data into baseband packets, manages connection status indicators, and composes and decodes Host Controller Interface (HCI) packets. In addition to these functions, it independently handles HCI event types and HCI command types.

The following transmit and receive functions are also implemented in the BBC hardware to increase reliability and security of the TX/ RX data before data is sent over the air:

- Symbol timing recovery, data deframing, Forward Error Correction (FEC), Header Error Control (HEC), Cyclic Redundancy Check (CRC), data decryption, and data dewhitening in the receiver

- Data framing, FEC generation, HEC generation, CRC generation, key generation, data encryption, and data whitening in the transmitter

#### 2.5.1 Frequency Hopping Generator

The frequency hopping sequence generator supports AFH by selecting the correct hopping channel number depending on the link controller state, Bluetooth clock, and device address.

#### 2.5.2 Link Control Layer

The link control layer is part of the Bluetooth link control functions that are implemented in dedicated logic in the Link Control Unit (LCU). This layer consists of the command controller that takes commands from the software, and other controllers that are activated or configured by the command controller to perform the link control tasks. There are two major states: STANDBY and CONNECTION. In addition, there are six substates: PAGE, PAGE SCAN, INQUIRY, INQUIRY SCAN, SNIFF, and HOLD.

# 3. CPU Subsystem

### 3.1 Cortex-M3™

The CYW20745 uses a Cortex M3. The CPU is clocked at up to 48 MHz. During idle time, the CPU is placed in a low-power state.

### 3.2 On-Chip Memories

The CYW20745 includes TBD KB of ROM and 120 KB of RAM. The ROM stores firmware for the headset application. The RAM stores temporary variables. An external EEPROM is used to store configuration and nonvolatile variables.

### 3.3 Watchdog Timer

The hardware incorporates a watchdog timer capable of resetting the chip. The watchdog timer ensures correct system operation.

#### 3.4 General-Purpose Timer

The general-purpose timer can be configured to operate either from the high-speed clock source or the Low-Power Oscillator (LPO). When operating from the LPO, the timer can wake the hardware from deep sleep when a timer event occurs.

#### 3.5 ARM® JTAG

The test mode pins can be configured to switch the CYW20745 to operate in ARM JTAG mode as shown in Table 2.

#### Table 2. Enabling ARM JTAG with the TM Pins

| Function         | TM1 | TM2 |

|------------------|-----|-----|

| Normal operation | 0   | 0   |

| ARM JTAG         | 1   | 0   |

| Reserved         | х   | 1   |

The I/O assignments in the ARM JTAG mode are provided in Table 3.

#### Table 3. JTAG Connections

| Signal | Pin   |

|--------|-------|

| ТСК    | GPIO5 |

| TDI    | GPIO8 |

| TDO    | GPIO7 |

| TMS    | GPIO6 |

| TRSTN  | RST_N |

### 3.6 External Reset

The CYW20745 has an integrated Power-On Reset (POR) circuit that resets all circuits to a known power-on state. This action can <u>also</u> be driven by an external reset signal that can be used to externally control the device, forcing it into a power-on reset state. The RST signal input is active low and has an internally programmable pull-up resistor (no connection is required in most applications).

When the reset signal is asserted (100  $\mu$ sec low on  $\overline{RST}$ ), the GPIOs are in the following states:

- GPIO\_13 = pulled down

- GPIO\_12 = pulled down

- GPIO\_11 = pulled up

- GPIO\_10 = pulled down

- GPIO\_9 = pulled down

- GPIO\_8 = pulled down

- GPIO\_7 = pulled up

- GPIO\_6 = pulled up

- GPIO\_5 = pulled up

- GPIO\_4 = pulled up

- GPIO\_3 = pulled up

- GPIO\_2 = pulled down

- GPIO\_1 = pulled down

- GPIO\_0 = pulled down

# 4. Power Management Unit

To reduce the external bill of materials, the CYW20745 integrated power management unit includes the following key features:

- Switching regulator

- Optimized for lithium-ion and Lithium Polymer batteries

- LDO regulators for noise isolation

- Battery charger

- LED drivers

- Low-battery detection

- Undervoltage lockout

- Short circuit protection

- On-chip temperature sensor

- Charger watchdog

**Caution!** The CYW20745 is designed for use with lithium secondary cell batteries. These batteries can become unsafe and ignite, rupture, explode, reach high temperatures, and leak acid. Special caution must be exercised in the design, manufacture, test, and use of the end product that incorporates this device. The CYW20745 has built-in features that are intended to reduce, but not eliminate, the chance of an unsafe condition. When using lithium batteries, it is strongly recommended that an external battery protection IC be used to manage charger overvoltage, discharge undervoltage, charger overcurrent, and discharge overcurrent. In addition, the lithium cells should have an integrated PTC, thermal fuse, vent, and or a separator. Consult the battery manufacturer for safety suggestions. Due to these system level usage and safety protections, Cypress accepts no responsibility for any injuries or damages sustained as a result of using this device. The customer assumes all attendant risk.

#### 4.1 Switching Regulator

The CYW20745 includes an integrated high-performance, buck-mode switching regulator optimized to work with single-cell lithiumion batteries.

The switching regulator includes the following capabilities and features:

- Direct power from a lithium-ion battery

- Programmable output voltage

- Programmable switching frequency

- Burst mode for a low quiescent current

- Pulse-Width Modulation (PWM) mode for a clean supply voltage in active mode

- Fast switching between burst and PWM modes

- Soft start-up

- Low start-up voltage (external enable with battery undervoltage lockout)

- Duty cycle limiting, up to 90% duty cycle

- Overcurrent protection

- Snubber to eliminate ringing or oscillation

- High efficiency

- Low quiescent current with no load

### 4.2 LDO Regulators

Multiple LDO regulators are included, each individually tailored to provide all of the required low-noise supply voltages for driving critical on-chip circuits.

There are four major linear regulators in the CYW20745—BT core/RF circuits, I/Os, audio codec, and speaker driver. A low-noise microphone bias supply is also provided.

#### 4.3 Battery Charger

The CYW20745 includes an integrated battery charger optimized for use with lithium-ion and lithium polymer batteries.

The battery charger's operation is based on a hardware state machine that runs separately from the CYW20745 baseband logic and Central Processing Unit (CPU). The charging algorithm parameters are configurable and can be tuned to optimize the charger's performance for specific batteries and charging power supplies. These parameters are stored in off-chip EEPROM or serial flash and are loaded into the charger state machine once the CPU boots and starts running.

Battery charger capabilities and features include:

- System operation while the battery is charging.

- A four-stage battery charge algorithm (pre-charge0, constant current, constant voltage, and recharge). The constant current phase supports programmable voltage and current levels. The number of programmable voltage and current levels is also programmable.

- Internal pass transistor for low-cost systems.

- Optional charger voltage regulation using external bipolar transistor for high-voltage charging systems

- Safety timers for each charge stage.

- Continuously running fault detectors (including battery overcurrent, battery overvoltage, and charger voltage errors)

- Temperature and voltage drop safety detectors

- Internal temperature sensor

- Low-power UVLO mode

- Fuel-gauge monitoring

- Power dissipation control

- Charger type detection

- Handles standard charge batteries from 30 mAh to 200 mAh and 3C fast charge batteries from 30 mAh to 130 mAh. Possibility of fast charging at 5C for batteries below 80 mAH.

- Handles standard carkit batteries (0.5C charge) from 30 mAh to 800 mAh.

- Can preserve the battery health by reducing recharge cycles (the CYW20745 chip sinks limited/reduced current from the battery when the charger is plugged in and the battery is fully charged).

- Integrated ADC for monitoring battery, temperature, and charger voltage.

#### 4.3.1 Charger Watchdog

A watchdog circuit in the charger block has been included to automatically reset the CYW20745 in the event of a firmware crash. The following details apply to watchdog timer operation:

- The watchdog timer is disabled at POR.

- By default, firmware will enable the watchdog timer during bootup. Once enabled, the watchdog timer cannot be disabled.

- The watchdog timer countdown starts immediately after a charger is plugged in.

- Once started, the watchdog countdown continues until a watchdog time-out triggers a baseband POR, unless firmware stops the watchdog before the timer completes its countdown.

- As long as a charger remains attached, the watchdog will remain inactive after a POR or after firmware stops the watchdog. The watchdog will be reactivated if a charger is removed and then reattached.

- The default setting for the watchdog timer is two seconds.

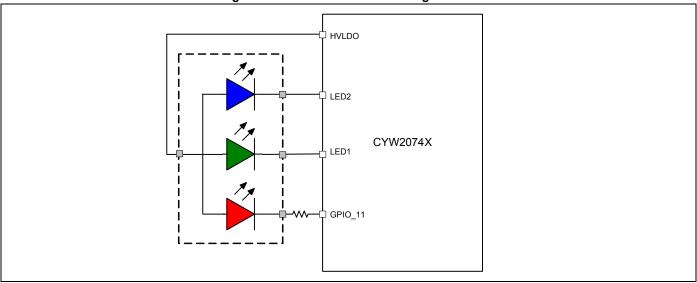

### 4.4 LED Drivers

The CYW20745 includes two integrated, constant-current LED drivers and one GPIO with PWM voltage control that can be used as a third LED driver.

LED driver capabilities and features include:

- Programmable drive current

- Low dropout voltage

- Current sinking driver with high voltage tolerance to allow connecting LEDs to the I/O power supply.

Figure 4 illustrates recommended LED connections to the CYW20745.

### Figure 4. Recommended LED Configuration6

# 5. Peripherals

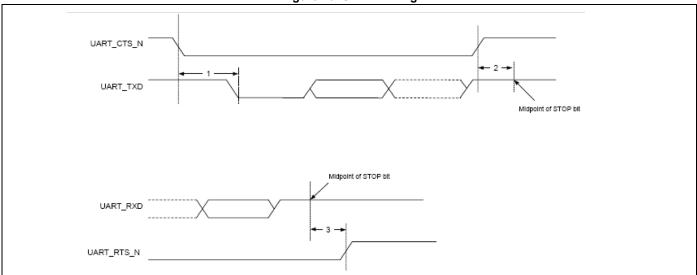

### 5.1 UART Interface

The UART physical interface is a standard, 4-wire interface (RX,TX, RTS, CTS) with a 9600 bps to 1.5 Mbps adjustable baud rate. The interface features an automatic baud rate detection capability to establish a proper baud rate selection. Alternatively, the baud rate may be preconfigured in the firmware. The CYW20745 has a 480-byte receive FIFO and a 480-byte transmit FIFO to support high data rates.

**Note**: By default, the UART is configured to operate over the USB connector (UART over USB). For more information on how to implement UART over USB, refer to *UART Communication Over USB Connector*, document number 2074X-AN60x-R.

#### Table 4. GPIO Assignment for the UART Interface

| Signal | Pin    |

|--------|--------|

| RXD    | GPIO0  |

| TXD    | GPIO1  |

| CTS    | GPIO2  |

| RTS    | GPIO13 |

The CYW20745 has the capability to perform XON/XOFF flow control and has hardware support for Serial Line Internet Protocol (SLIP). It also has the capability to perform wake-on-activity. When the chip is in a low-power sleep mode, activity on the RX or CTS inputs can wake the chip.

The baud rate of the CYW20745 UART is controlled by two registers. The first, called the DLBR register, is a UART clock divisor that divides the 24 MHz reference clock by an integer multiple of 16. The second, called the DHBR register, is a baud rate adjustment that is used to specify a number of 24 MHz clock cycles to stuff in the first or second half of each bit time. Up to eight 24 MHz clock cycles can be inserted into the first half of each bit time, and up to eight 24 MHz clock cycles can be inserted into the second half of each bit time.

When setting the baud rate manually, the UART clock divisor is an 8-bit value that is stored as 256 - desired divisor. For example, a desired divisor of 13 is stored as 256 - 13 = 243 = 0 xF3.

The baud rate adjustment is also an 8-bit value, of which the 4 most significant bits are the number of additional clock cycles to insert in the first half of each bit time, and the 4 least significant bits are the number of clock cycles to insert in the second half of each bit time. If either of these two values exceeds 8, they are rounded to 8.

Table 5 contains example values to generate common baud rates.

# Table 5. Common Baud Rate Examples

| Desired Baud<br>Rate in bps | UART Clock Divisor (256 –<br>Desired Divisor) | Baud Rate Adjust-<br>ment (High Nibble) | Baud Rate Adjust-<br>ment<br>(Low Nibble) | Actual CYW20745<br>Baud Rate in bps | Percentage Er-<br>ror |

|-----------------------------|-----------------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------|-----------------------|

| 1500000                     | 0xFF                                          | 0x00                                    | 0x00                                      | 1500000                             | 0.00                  |

| 921600                      | 0xFF                                          | 0x05                                    | 0x05                                      | 923077                              | 0.16                  |

| 460800                      | 0xFD                                          | 0x02                                    | 0x02                                      | 461538                              | 0.16                  |

| 230400                      | 0xFA                                          | 0x04                                    | 0x04                                      | 230796                              | 0.17                  |

| 115200                      | 0xF3                                          | 0x00                                    | 0x00                                      | 115385                              | 0.16                  |

| 57600                       | 0xE6                                          | 0x00                                    | 0x00                                      | 57692                               | 0.16                  |

| 38400                       | 0xD9                                          | 0x01                                    | 0x00                                      | 38400                               | 0.00                  |

| 28800                       | 0xCC                                          | 0x00                                    | 0x00                                      | 28846                               | 0.16                  |

| 19200                       | 0xB2                                          | 0x01                                    | 0x01                                      | 19200                               | 0.00                  |

| 14400                       | 0x98                                          | 0x00                                    | 0x00                                      | 14423                               | 0.16                  |

| 9600                        | 0x64                                          | 0x02                                    | 0x02                                      | 9600                                | 0.00                  |

Normally, the UART baud rate is set by the parameters stored in the EEPROM or serial flash, or by automatic baud rate detection, and the host does not need to adjust the baud rate. The CYW20745 UART will operate correctly with the host UART as long as the combined baud rate error of the two devices is within ±5%.

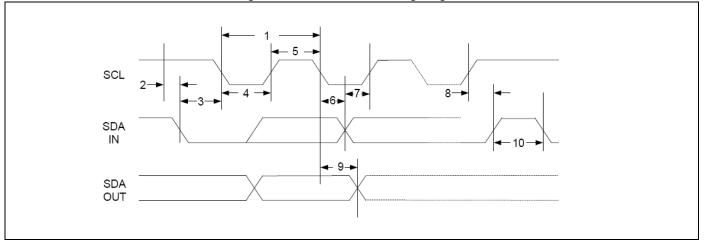

#### 5.2 BSC Interface

The CYW20745 includes dedicated hardware for implementing a 2-wire interface used to connect to an off-chip serial EEPROM. The EEPROM is required to store configuration parameters as well as pairing information. Support is available for 100 Kbps and 400 Kbps data rate configurations. The default data rate is 100 Kbps. In this context, Kbps = 1000 bits per second.

**Note**: The Broadcom Serial Control (BSC) bus is Philips® I<sup>2</sup>C compatible.

#### 5.3 SPI Interface

The Serial Peripheral Interface (SPI) is a high-speed, synchronous serial interface that can be used for interfacing with other devices. A full-duplex DMA channel is available for low overhead SPI control. The SPI interface supports several modes of operation:

- 4-wire mode—interface includes clock, chip select, data in, and data out. This is the standard mode of operation.

- 3-wire mode—interface includes clock, chip select, and one bidirectional data line for devices that support 3-wire mode of operation on SPI.

- Master mode—the SPI can be configured for master mode operation up to a maximum frequency of 24 MHz.

- Slave mode—the SPI can be configured for slave mode operation up to 48 MHz.

### 5.4 GPIO

The CYW20745 has three GPIOs for the user interface input. This allows for up to three buttons on the headset.

#### **Table 6. GPIO Assignment for Buttons**

| Signal        | Pin         |

|---------------|-------------|

| Multifunction | GPIO3/WAKEB |

| Volume up     | GPIO8       |

| Volume down   | GPIO9       |

# 6. Audio

### 6.1 Codec

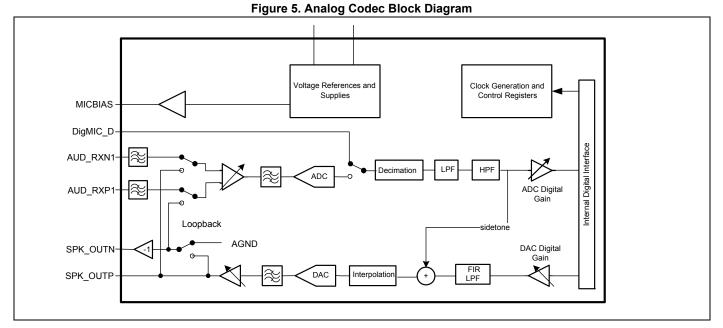

Figure 5 shows the analog codec block diagram.

#### 6.1.1 DAC and Headset Amplifier

The CYW20745 DAC and headset amplifiers include the following capabilities and features:

- **\blacksquare** 32 $\Omega$  and 16 $\Omega$  speaker-impedance support

- Differential load connections

- 18 dB analog gain control

- Pop reduction circuit at power-up/down

- Several power modes

- 8 kHz and 16 kHz sample rates

#### 6.1.2 Preamplifier and ADC

The CYW20745 preamplifier and ADC include the following capabilities and features:

- Wide dynamic range

- Optional in-band analog High-Pass Filter (HPF) for increased wind noise tolerance

- Differential and single-ended modes

- Microphone preamplifier

- Low-noise microphone bias generator

- Configurable HPF in the microphone path

- 8 kHz and 16 kHz sample rates

#### 6.1.3 Sample Rate Adaptation

The digital rate adapter allows for up to a 5 percent adjustment and is automatically controlled by a sophisticated rate tracking and adaptation algorithm.

### 6.2 Speech Codecs

In addition to pass-through (no compression/decompression), the CYW20745 supports the following speech codecs:

- 8 kHz CVSD

- 8 kHz A-law

- 8 kHz µ-law

### 6.3 A2DP Codec

The CYW20745 supports the following A2DP codec settings:

- SBC Sampling Frequency—48 kHz, 44.1 kHz, 32 kHz, and 16 kHz are the supported sampling frequencies.

- Channel Mode—Mono, Dual, Stereo, and Joint Stereo modes are supported.

- Bit Pools:

- □ Joint Stereo: 30-249

- □ Dual: 16–75

- Mono: 14–128

- □ Stereo: 30–250

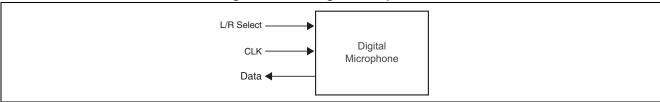

#### 6.4 Digital Microphone Support

The interface drawing and definition of the microelectromechanical systems (MEMS) digital microphone is shown in Figure 6. The output from the digital microphone is a binary bit sequence. A 3 MHz clock must be supplied to the digital microphone from the CYW20745. L/R select is used to define the clock edge on which the data from the microphone is output. L/R select is tied to ground because the interface is designed to support only a single digital microphone.

### Figure 6. MEMS Digital Microphone Interface

#### Table 7. MEMS Digital Microphone Interface

| Signal Name | Description                                                                                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------|

| Data        | Microphone binary data output (connect to GPIO)                                                                                  |

| CLK         | Microphone external clock input (connect to GPIO, 3 MHz, 50% duty cycle)                                                         |

| L/R select  | Microphone input that defines which edge of the clock signal will be used to trigger data output; typically connected to ground. |

# 7. Frequency References

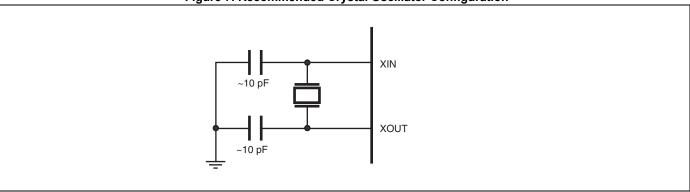

The CYW20745 uses two different frequency references for normal and low-power operational modes. An external crystal is used to generate all radio frequencies and clocks used during normal operation. A fully integrated internal LPO is used to supply the clock during low-power modes.

### 7.1 Crystal Interface and Clock Generation

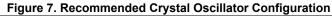

The CYW20745 uses a 26 MHz crystal as the primary reference frequency. Figure 7 illustrates the recommended configuration for the crystal oscillator, including all external components.

### 7.2 Low-Power Oscillator

To enable low-power operating modes, an internal LPO is included on the CYW20745. The oscillator is calibrated automatically by the hardware.

# 8. Operation

### 8.1 CYW20745 Modes of Operation

Specific user, and other monitored system events, determine the mode in which the CYW20745 operates. Each supported operating mode is designed to perform the desired function, while minimizing power consumption.

The CYW20745 supports the following operating modes:

| Active mode           | The fully functional mode of the chip in which the headset is in a connected state and has an active call.                                                                                                                                                                                                                                                              |

|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Standby mode          | In standby mode, HS is in a connected state, and there is no active call, but the HS is waiting for an incoming or outgoing call.                                                                                                                                                                                                                                       |

| Sleep mode            | This is a temporary chip mode in which certain blocks are switched off (for example, radio, codec, and so on), but the software is in a state where it can quickly turn on all blocks and enter a fully functional mode. Typically software switches to this mode between bursts of activity (radio or signal processing) to conserve power in active or standby modes. |

| Deep Sleep (off) mode | In this mode, leakage current flows from the battery, and the chip performs no functions. To escape this mode, a user button-press event or charger plug-in event must occur.                                                                                                                                                                                           |

| Charging mode         | The CYW20745 operates in the charging mode when the charger is plugged in. All activities related to battery charging, monitoring, and safety features are performed in this mode.                                                                                                                                                                                      |

# 9. Pin Assignments

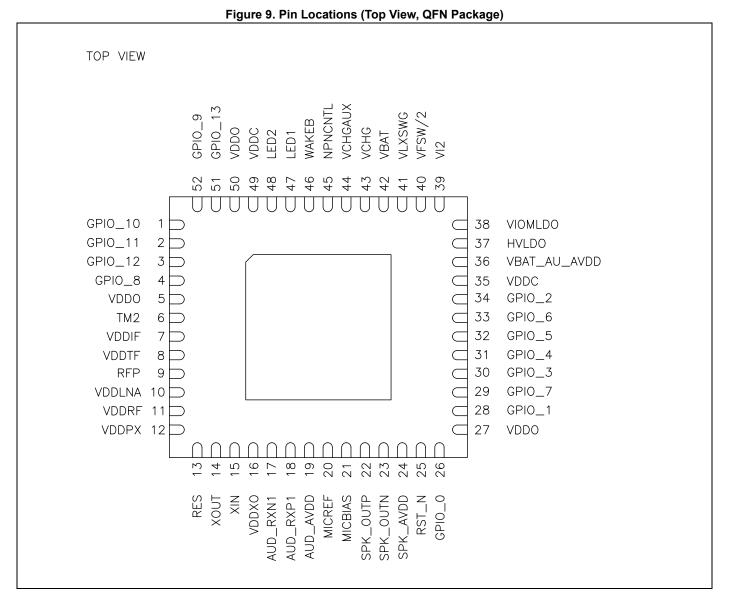

Table 8 lists pin assignments on the CYW20745 for the WFBGA package.Table 9 lists pin assignments on the CYW20745 for the QFN package.

Table 8. CYW20745 Pin Assignments (WFBGA Package)

| Pin Name | Pin Number     | I/O | Power Domain | Description                                                                                                           |

|----------|----------------|-----|--------------|-----------------------------------------------------------------------------------------------------------------------|

| AUD_AVDD | E6             | I   | AUD_AVDD     | Audio codec analog power                                                                                              |

| AUD_AVSS | F5, G4, H4, H8 | Ι   | AUD_AVSS     | Audio codec analog ground                                                                                             |

| AUD_RXN1 | H5             | I   | AUD_AVDD     | Audio codec microphone differential negative input channel.                                                           |

| AUD_RXP1 | G5             | Ι   | AUD_AVDD     | Audio codec microphone differential positive input channel.                                                           |

| NC       | H6             | _   | -            | No connect                                                                                                            |

| NC       | G6             | _   | -            | No connect                                                                                                            |

| AUD_AVSS | B8             | Ι   | AVSS         | Charger. Analog ground                                                                                                |

| NPNCNTL  | C7             | 0   | VCHG         | Base control for external PNP driver transistor through an NPN transistor, used for handling high charging voltage.   |

| GPIO_0   | F8             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_1   | E7             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_2   | C8             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_3   | F10            | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_4   | E9             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_5   | D5             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_6   | D7             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_7   | F9             | I/O | VDDO         | General-purpose I/O, or mux into ADC                                                                                  |

| GPIO_8   | D4             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_9   | C4             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_10  | A1             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_11  | B2             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_12  | B3             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| GPIO_13  | B5             | I/O | VDDO         | General-purpose I/O                                                                                                   |

| HVLDO    | C10            | 0   | AVDD         | Voltage supply for I/Os. Voltage output pin from HVLDO.<br>Analog power supply to drive digital I/O, flash, and LEDs. |

| LED1     | A6             | 0   | VBAT         | Output driver for LED. Connect the cathode of LED1. Anode can be connected to HVLDO.                                  |

| LED2     | B6             | 0   | VBAT         | Output driver for LED. Connect the cathode of LED2. Anode can be connected to HVLDO.                                  |

| MICBIAS  | G7             | 0   | MICAVDD      | Microphone bias output                                                                                                |

| MICREF   | H7             | Ι   | ACDAVDD      | Microphone reference voltage                                                                                          |

| RES      | G2             | 0   | VDDXO        | External calibration resistor (connect 15K, 1% to ground)                                                             |

| RFP      | E1             | I/O | VDD_RF       | RF I/O port, connect to antenna                                                                                       |

| RST      | G10            | I   | VDDO         | Power-on reset, active low                                                                                            |

| SPK_AVDD | H10            | Ι   | SPKAVDD      | Speaker analog power                                                                                                  |

| SPK_AVSS | G8             | I   | SPKAVSS      | Speaker ground                                                                                                        |

| SPK_OUTN | H9             | 0   | SPKAVDD      | Speaker differential negative output channel                                                                          |

| SPK_OUTP | G9             | 0   | SPKAVDD      | Speaker differential positive output channel                                                                          |

| TM1      | C2             | I   | VDDO         | Test mode pin (connect to ground)                                                                                     |

| TM2      | B1             | I   | VDDO         | Test mode pin (connect to ground)                                                                                     |

#### Table 8. CYW20745 Pin Assignments (WFBGA Package) (Cont.)

| Pin Name     | Pin Number            | I/O | Power Domain | Description                                                                                                                                                                         |

|--------------|-----------------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VBAT         | A7                    | I   | VBAT         | Battery positive supply terminal pin                                                                                                                                                |

| VBAT_AU_AVDD | D9                    | Ι   | VBAT         | Power input for audio LDO and HVLDO—powers from battery as VBAT pin                                                                                                                 |

| VCHG         | A5                    | Ι   | VCHG         | Charger supply input                                                                                                                                                                |

| VCHGAUX      | A4                    | Ι   | VCHG         | Power to the charger control system                                                                                                                                                 |

| VDDC         | A3, D10               | I   | VDDC         | 1.2V core power input. Tie to V12 on PCB.                                                                                                                                           |

| VDDIF        | C1                    | I   | VDDIF        | Power to the IF circuit. Tie to V12 on PCB.                                                                                                                                         |

| VDDLNA       | F1                    | I   | VDDLNA       | Power to the LNA. Tie to V12 on PCB.                                                                                                                                                |

| VDDO         | A2, E10               | I   | VDDO         | 3.3V digital I/O power input. Tie to AVDD on PCB.                                                                                                                                   |

| VDDPX        | H1                    | Ι   | VDDPLL       | RF PLL supply voltage. Tie to V12 on PCB.                                                                                                                                           |

| VDDTF        | D1                    | I   | VDDTF        | PA supply voltage. Tie on PCB to V12 pin for Class 2 or to external power source up to 2.5V for Class 1.                                                                            |

| VDDRF        | G1                    | Ι   | VDDRF        | RF and VCO power supply. Tie to V12 on PCB.                                                                                                                                         |

| VDDXO        | H2                    | I   | VDDXO        | Crystal oscillator power supply. Tie to V12 on PCB.                                                                                                                                 |

| VFSW         | A10                   | I   | VBAT         | PMU switching regulator output voltage feedback. Feedback network input of regulated switcher output voltage.                                                                       |

| VIOMLDO      | B9                    | 0   | V12          | Main LDO supply decoupling pin                                                                                                                                                      |

| VLXSWG       | A9                    | 0   | VBAT         | PMU switching regulator inductor terminal. SWREG inductor terminal.                                                                                                                 |

| V12          | B10                   | 0   | V12          | Main LDO output 1.2V to digital power                                                                                                                                               |

| VSS          | C9, D2, E3, E8,<br>F2 | I   | VSS          | Digital radio ground                                                                                                                                                                |

| VSSP         | A8                    | I   | VSS          | PMU ground                                                                                                                                                                          |

| WAKEB        | B7                    | I   | AVDD_OUT     | PMU wake-up and shut-down pin. MIA-LITE wakeup/system power-down signal. Connects to button switch. Internal pull-up with 0 = button activated. Active low level initiates wake-up. |

| XOUT         | G3                    | 0   | VDDXO        | XTAL out                                                                                                                                                                            |

| XIN          | H3                    | Ι   | VDDXO        | XTAL in                                                                                                                                                                             |

#### Figure 8 shows the pin locations on the CYW20745 WFBGA package.

|   |              | 0         | 0         |              |           |           |           |           | 0                | 10         |   |

|---|--------------|-----------|-----------|--------------|-----------|-----------|-----------|-----------|------------------|------------|---|

| А | 1<br>GPIO_10 | 2<br>VDDO | 3<br>VDDC | 4<br>VCHGAUX | 5<br>VCHG | 6<br>LED1 | 7<br>VBAT | 8<br>VSSP | 9<br>VLXSWG      | 10<br>VFSW | A |

| в | TM2          | GPIO_11   | GPIO_12   |              | GPIO_13   | LED2      | WAKEB     | AVSS      | VIOMLDO          | V12        | в |

| с | VDDIF        | TM1       |           | GPIO_9       |           |           | NPNCNTL   | GPIO_2    | VSS              | HVLDO      | с |

| D | VDDTF        | VSS       |           | GPIO_8       | GPIO_5    |           | GPIO_6    |           | VBAT_AU_<br>AVDD | VDDC       | D |

| Е | RFP          |           | VSS       |              |           | AUD_AVDD  | GPIO_1    | VSS       | GPIO_4           | VDDO       | Е |

| F | VDDLNA       | VSS       |           |              | AUD_AVSS  |           |           | GPIO_0    | GPIO_7           | GPIO_3     | F |

| G | VDDRF        | RES       | XOUT      | AUD_AVSS     | AUD_RXP1  | NC        | MICBIAS   | SPK_AVSS  | SPK_OUTP         | RST_N      | G |

| н | VDDPX        | VDDXO     | XIN       | AUD_AVSS     | AUD_RXN1  | NC        | MICREF    | AUD_AVSS  | SPK_OUTN         | SPK_AVDD   | н |

| . | 1            | 2         | 3         | 4            | 5         | 6         | 7         | 8         | 9                | 10         | - |

### Table 9. CYW20745 Pin Assignments (QFN Package)

| Pin Name     | Pin Number | I/O | Power Domain | Description                                                                                                           |

|--------------|------------|-----|--------------|-----------------------------------------------------------------------------------------------------------------------|

| AUD_AVDD     | 19         | I   | AUD_AVDD     | Audio codec analog power                                                                                              |

| AUD_RXN1     | 17         | I   | AUD_AVDD     | Audio codec microphone differential negative input channel.                                                           |

| AUD_RXP1     | 18         | I   | AUD_AVDD     | Audio codec microphone differential positive input channel.                                                           |

| NPNCNTL      | 45         | 0   | VCHG         | Base control for external PNP driver transistor through an NPN transistor, used for handling high charging voltage.   |

| GPIO_0       | 26         | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_1       | 28         | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_2       | 34         | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_3       | 30         | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_4       | 31         | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_5       | 32         | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_6       | 33         | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_7       | 29         | I/O | VDDO         | General purpose I/O, or mux into ADC                                                                                  |

| GPIO_8       | 4          | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_9       | 52         | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_10      | 1          | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_11      | 2          | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_12      | 3          | I/O | VDDO         | General purpose I/O                                                                                                   |

| GPIO_13      | 51         | I/O | VDDO         | General purpose I/O                                                                                                   |

| HVLDO        | 37         | 0   | AVDD         | Voltage supply for I/Os. Voltage output pin from HVLDO.<br>Analog power supply to drive digital I/O, flash, and LEDs. |

| LED1         | 47         | 0   | VBAT         | Output driver for LED. Connect the cathode of LED1. Anode can be connected to HVLDO.                                  |

| LED2         | 48         | 0   | VBAT         | Output driver for LED. Connect the cathode of LED2. Anode can be connected to HVLDO.                                  |

| MICBIAS      | 21         | 0   | MICAVDD      | Microphone bias output                                                                                                |

| MICREF       | 20         | I   | ACDAVDD      | Microphone reference voltage                                                                                          |

| RES          | 13         | 0   | VDDXO        | External calibration resistor (connect 15K, 1% to ground)                                                             |

| RFP          | 9          | I/O | VDD_RF       | RF I/O port, connect to antenna                                                                                       |

| RST          | 25         | I   | VDDO         | Power-on reset, active low                                                                                            |

| SPK_AVDD     | 24         | I   | SPKAVDD      | Speaker analog power                                                                                                  |

| SPK_OUTN     | 23         | 0   | SPKAVDD      | Speaker differential negative output channel                                                                          |

| SPK_OUTP     | 22         | 0   | SPKAVDD      | Speaker differential positive output channel                                                                          |

| TM2          | 6          | I   | VDDO         | Test mode pin (connect to ground)                                                                                     |

| VBAT         | 42         | I   | VBAT         | Battery positive supply terminal pin                                                                                  |

| VBAT_AU_AVDD | 36         | I   | VBAT         | Power input for audio LDO and HVLDO—powers from battery as VBAT pin                                                   |

| VCHG         | 43         | I   | VCHG         | Charger supply input                                                                                                  |

| VCHGAUX      | 44         | I   | VCHG         | Power to the charger control system                                                                                   |

| VDDC         | 35, 49     | I   | VDDC         | 1.2V core power input. Tie to V12 on PCB.                                                                             |

| VDDIF        | 7          | I   | VDDIF        | Power to the IF circuit. Tie to V12 on PCB.                                                                           |

| VDDLNA       | 10         | I   | VDDLNA       | Power to the LNA. Tie to V12 on PCB.                                                                                  |

| VDDO         | 5,27,50    | I   | VDDO         | 3.3V digital I/O power input. Tie to AVDD on PCB.                                                                     |

| VDDPX        | 12         | I   | VDDPLL       | RF PLL supply voltage. Tie to V12 on PCB.                                                                             |

### Table 9. CYW20745 Pin Assignments (QFN Package) (Cont.)

| Pin Name | Pin Number | I/O | Power Domain | Description                                                                                                                                                                         |

|----------|------------|-----|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VDDTF    | 8          | Ι   | VDDTF        | PA supply voltage. Tie on PCB to V12 pin for Class 2 or to external power source up to 2.5V for Class 1.                                                                            |

| VDDRF    | 11         | I   | VDDRF        | RF and VCO power supply. Tie to V12 on PCB.                                                                                                                                         |

| VDDXO    | 16         | Ι   | VDDXO        | Crystal oscillator power supply. Tie to V12 on PCB.                                                                                                                                 |

| VFSW     | 40         | Ι   | VBAT         | PMU switching regulator output voltage feedback. Feedback network input of regulated switcher output voltage.                                                                       |

| VIOMLDO  | 38         | 0   | V12          | Main LDO supply decoupling pin                                                                                                                                                      |

| VLXSWG   | 41         | 0   | VBAT         | PMU switching regulator inductor terminal. SWREG inductor terminal.                                                                                                                 |

| V12      | 39         | 0   | V12          | Main LDO output 1.2V to digital power                                                                                                                                               |

| VSS      | Center PAD | I   | VSS          | Digital radio ground                                                                                                                                                                |

| WAKEB    | 46         | Ι   | AVDD_OUT     | PMU wake-up and shut-down pin. MIA-LITE wakeup/system power-down signal. Connects to button switch. Internal pull-up with 0 = button activated. Active low level initiates wake-up. |

| XOUT     | 14         | 0   | VDDXO        | XTAL out                                                                                                                                                                            |

| XIN      | 15         | I   | VDDXO        | XTAL in                                                                                                                                                                             |

Figure 9 shows the pin locations on the CYW20745 QFN package.

# 10. Specifications

### **10.1 Environmental Specifications**

Environmental specifications for the CYW20745 are listed below:

- Operating temperature range (see "Ordering Information" on page 41)

- Storage temperature range: -40°C to +125°C

- RoHS lead-free compliance

### **10.2 Maximum Rating Specifications**

Note: All data reported in this section are derived from system characterization.

#### **Table 10. Absolute Maximum Electrical Ratings**

| Rating                                                                  | Symbol            | Value                                    | Unit |

|-------------------------------------------------------------------------|-------------------|------------------------------------------|------|

| Maximum DC supply voltage for I/O                                       | VDDO              | 3.8                                      | V    |

| Maximum DC supply voltage for charger                                   | VCHG              | 6.5                                      | V    |

| Maximum voltage on input or output pin                                  | Vimax             | Domain supply voltage <sup>a</sup> + 10% | V    |

| Maximum transient voltage on input or output pin, 10% maximum duty time | Vimaxt            | 4.1                                      | V    |

| Minimum voltage on input or output pin                                  | Vimin             | VSS – 0.3v                               | V    |

| Maximum voltage on LED 2 pin                                            | VLED2-max         | 4.1                                      | V    |

| Storage temperature range                                               | Tstg              | -40 to +125                              | °C   |

| Maximum battery input voltage                                           | VBAT              | 4.5                                      | V    |

| Maximum charger power dissipation                                       | Pmax(VCHG – VBAT) | 390                                      | mW   |

a. Refer to Table 8: "CYW20745 Pin Assignments (WFBGA Package)," on page 20, for the appropriate power domain.

**Caution!** Voltage should never be applied to any I/O pins if VDDO is not applied. I/O pins (pins listed with VDDO as the power domain) should never be actively driven high or externally pulled high.

#### **10.3 PMU Specifications**

<u>(</u>)

Note: All data reported in this section are derived from system characterization.

#### Table 11. Typical Power Supply Output Voltage

| Power Outputs         | Description                                                                            | Condition    | Typical      | Unit |

|-----------------------|----------------------------------------------------------------------------------------|--------------|--------------|------|

| VLXSWG                | Switching regulator output looping back through the VFSW pin as the system power input | Programmable | 1.2, 1.3–1.6 | V    |

| AUD_AVDD/<br>SPK_AVDD | Audio and speaker power supply and decoupling                                          | _            | 2.7          | V    |

| V12                   | RF, XTAL, and core power supply output                                                 | -            | 1.2          | V    |

| AVDD                  | Voltage supply for charger PMU analog circuits and MIC bias                            | -            | 3.3          | V    |

#### Table 12. Switching Regulator Characteristics

| Property                             | Conditions      | Minimum | Typical | Maximum | Unit |

|--------------------------------------|-----------------|---------|---------|---------|------|

| Input voltage range                  | Operating range | 3.1     | 3.7     | 4.2     | V    |

| Switching frequency                  | -               | -       | 2.8     | -       | MHz  |

| Quiescent current                    | Burst mode      | -       | 80      | -       | μA   |

| Power-down current                   | -               | -       | 500     | _       | nA   |

| Output current burst mode efficiency | 3 mA load       | 80      | -       | -       | %    |

| Output current PWM mode, peak        | -               | -       | 10      | 24.2    | mA   |

| Output current PWM mode efficiency   | 30 mA           | -       | 90      | _       | %    |

| Start-up input voltage               | 0–5 mA load     | -       | 2.5     | _       | V    |

| External output inductor             | -               | -       | 10      | -       | μH   |

| External output capacitor            | -               | -       | 4.7     | _       | μF   |

| Output voltage ripple                | PWM mode        | -       | -       | 20      | mVpp |

| Output voltage ripple                | Burst mode      | _       | _       | 100     | mVpp |

#### Table 13. Battery Charger

| Property                                                               | Condition(s)/Description                                                                        | Minimum | Typical/<br>Default | Maximum | Unit    |

|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|---------|---------------------|---------|---------|

| Charging temperature range                                             | -                                                                                               | -       | 0–45 <sup>a</sup>   | -       | °C      |

| Charger active power supply consumption without battery charge current | Vch > 4.2V                                                                                      | -       | -                   | 2       | mA      |

| Vch to Vbat leakage                                                    | Charger input is 0V.<br>Vbat is 3.6V.                                                           | -       | 113                 | -       | μΑ      |

| Charger input voltage                                                  | Average voltage                                                                                 | 4.5     | 5.0                 | 6.5     | V       |

| Battery overvoltage threshold                                          | Programmable in 100 mV steps                                                                    | -       | 4.3                 | -       | V       |

| Constant voltage regulation                                            | Programmable in 100 mV steps                                                                    | -       | 4.2                 | -       | V       |

| Voltage regulation accuracy                                            | After trimming, 25°C                                                                            | _       | ±1                  | _       | %       |

| Constant current accuracy                                              | -                                                                                               | ±20     | -                   | _       | %       |

| Precharge safety timer, T0                                             | -                                                                                               | _       | 60                  | _       | minutes |

| Constant current <sup>b</sup>                                          | Programmable to values from<br>10 mA to 400 mA                                                  | -       | 50                  | -       | mA      |

| Constant current safety timer, T2                                      | Programmable from 20 minutes to 300 minutes                                                     | -       | 120                 | _       | minutes |

| Constant voltage safety timer, T3                                      | Programmable from 30 minutes to 4 hours                                                         | -       | 105                 | _       | minutes |

| Taper current                                                          | Programmable                                                                                    | _       | 20                  | _       | mA      |

| Timer accuracy                                                         | -                                                                                               | _       | ±25                 | _       | %       |

| Shutoff offset                                                         | Minimum difference with battery<br>voltage for starting the charge:<br>Vcharger > Vbat + offset | _       | 340                 | -       | mV      |

a. Charging temperature range can be configured through firmware. High and low threshold are configured separately: minimum up to -11°C, maximum up to +58°C. Refer to Broadcom application note 2074X-AN70x-R for information on configuring the charging temperature range.

b. Refer to Broadcom application note 2074X-AN70x-R for information on configuring the constant current.

### Table 14. Charger UVLO/POR

| Property                            | Conditions         | Minimum | Typical | Maximum | Unit |

|-------------------------------------|--------------------|---------|---------|---------|------|

| Charger UVLO low-voltage threshold  | Decreasing voltage | _       | 3.98    | _       | V    |

| Charger UVLO high-voltage threshold | Increasing voltage | -       | 4.17    | -       | V    |

#### Table 15. Battery UVLO

| Property                                 | Conditions         | Minimum | Typical | Maximum | Unit |

|------------------------------------------|--------------------|---------|---------|---------|------|

| Vbat undervoltage low threshold, lithium | Decreasing voltage | -       | 3.0     | -       | V    |

### Table 16. Low Battery Interrupt<sup>a</sup>

| Property                       | Conditions   | Typical | Unit |

|--------------------------------|--------------|---------|------|

| Low-battery threshold          | Programmable | 3.40    | V    |

| Critical low-battery threshold | Programmable | 3.16    | V    |

a. Refer to Broadcom application note 2074X-AN70x-R for information on configuring the threshold.

#### Table 17. LED Driver 1 and 2

| Property            | Conditions                   | Minimum | Typical | Maximum | Unit |

|---------------------|------------------------------|---------|---------|---------|------|

| Output sink current | Programmable in 0.8 mA steps | 0.8     | 2.3     | 6       | mA   |

| Current tolerance   | -                            | -20     | -       | 20      | %    |

### 10.4 General I/O

Note: All data reported in this section are derived from system characterization.

#### Table 18. General I/O Electrical Characteristics

| Symbol | Property                  | Minimum    | Typical | Maximum | Unit | Test Conditions   |

|--------|---------------------------|------------|---------|---------|------|-------------------|

| VIL    | Low-level input voltage   | -          | _       | 0.8     | V    | For 3.0–3.3V      |

| VIH    | High-level input voltage  | 2          | -       | —       | V    | For 3.0–3.3V      |

| VOL    | Low-level output voltage  | -          | _       | 0.4     | V    | IOL = 2 mA        |

| VOH    | High-level output voltage | VDDO - 0.4 | -       | -       | V    | IOH = 2 mA        |

| IOL    | Low-level output current  | -          | —       | 3       | mA   | VOL = 0.25V       |

| IOH    | High-level output current | _          | _       | 3       | mA   | VOH = IOVDD – 0.1 |

| II     | Input leakage current     | -          | _       | 0.25    | μA   | -                 |

| RPU    | Pull-up resistor          | _          | 60      | —       | kΩ   | -                 |

| RPD    | Pull-down resistor        | _          | 60      | _       | kΩ   | -                 |

# 10.5 RF Specifications

Note: All data reported in this section are derived from system characterization.

10.5.1 Receiver

### Table 19. Receiver RF Specifications

| Property                                                   | Minimum | Typical <sup>a</sup> | Maximum <sup>b</sup> | Unit |

|------------------------------------------------------------|---------|----------------------|----------------------|------|

| Receiver Section                                           |         | •                    |                      |      |

| Frequency range                                            | 2402    | -                    | 2480                 | MHz  |

| Rx Sensitivity                                             |         | •                    |                      |      |

| GFSK, 0.1% BER, 1 Mbps                                     | -       | -89.5                | -                    | dBm  |

| pi/4-DQPSK, 0.01% BER, 2Mbps                               | -       | -91.5                | -                    | dBm  |