### **VECANA01**

www.ti.com

# 10-Channel, 12-Bit DATA ACQUISITION SYSTEM

#### **FEATURES**

- 10 FULLY DIFFERENTIAL INPUTS

- 5 SIMULTANEOUS SAMPLED CHANNELS PLUS 2 SYNCHRONIZED SAMPLING CHANNELS

- 3 SYNCHRONIZED 12-BIT ADCs

- 12.8µs THROUGHPUT RATE

- DIGITALLY SELECTABLE INPUT RANGES

- +5V POWER SUPPLIES

- SERIAL DIGITAL INPUT/OUTPUTS

- 7 SIGN AND 3 DIGITALLY PROGRAMMABLE WINDOW COMPARATOR

#### DESCRIPTION

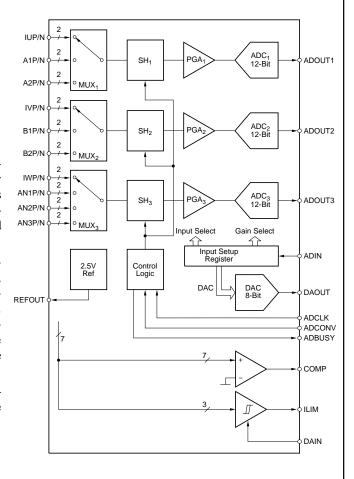

The VECANA01 consists of three 12-bit analog-to-digital converters preceded by five simultaneously operating sample-hold amplifiers, and multiplexers for 10 differential inputs. The ADCs have simultaneous serial outputs for high speed data transfer and data processing.

The VECANA01 also offers a programmable gain amplifier with programmable gains of 1.0V/V, 1.25V/V, 2.5V/V, and 5.0V/V. Channel selection and gain selection are selectable through the serial input control word. The high through put rate is maintained by simultaneously clocking in the 13-bit input control word for the next conversion while the present conversions are clocked out.

The part also contains an 8-bit digital-to-analog converter whose digital input is supplied as part of the input control word.

#### **APPLICATIONS**

- AC MOTOR SPEED CONTROLS

- THREE PHASE POWER CONTROL

- UNINTERRUPTABLE POWER SUPPLIES

- VIBRATION ANALYSIS

## **SPECIFICATIONS**

At  $V_{ANA+}$  = +5V,  $V_{ANA-}$  = -5V,  $V_{DIG+}$  = +5V,  $V_{DIG-}$  = -5V, and  $T_A$  = -40°C to +85°C, using internal reference,  $f_{CLOCK}$  = 1.25MHz.

#### **ANALOG-TO-DIGITAL CONVERTER CHANNELS**

|                                                    |                                      |          | VECANA01N        |            | UNITS                |  |

|----------------------------------------------------|--------------------------------------|----------|------------------|------------|----------------------|--|

| PARAMETER                                          | CONDITIONS                           | MIN      | TYP              | MAX        |                      |  |

| RESOLUTION                                         |                                      | 12       |                  |            | Bit                  |  |

| ANALOG INPUT                                       |                                      |          |                  |            |                      |  |

| Full Scale Voltage, Differential                   | G = 1.0V/V                           |          | ±2.5             |            | V                    |  |

|                                                    | G = 1.25V/V                          |          | ±2.0             |            | V                    |  |

|                                                    | G = 2.5V/V                           |          | ±1.0             |            | V                    |  |

|                                                    | G = 5.0V/V                           |          | ±0.5             |            | V                    |  |

| Common-Mode Voltage                                |                                      | ±0.5     | See Table VII    |            | V                    |  |

| Impedance                                          |                                      |          | 10 <sup>12</sup> |            | Ω                    |  |

| Capacitance                                        |                                      |          | 20               |            | pF                   |  |

| THROUGHPUT SPEED                                   | OLIK 4.05MU-                         |          |                  | 40.4       |                      |  |

| Conversion Time                                    | CLK = 1.25MHz                        |          |                  | 10.4       | μs                   |  |

| Complete Cycle                                     | Acquire and Convert                  | 78       |                  | 12.8       | μs                   |  |

| Throughput Rate                                    |                                      | 78       |                  |            | kHz                  |  |

| SAMPLING DYNAMICS                                  |                                      |          | 0.4              |            |                      |  |

| S/H Droop Rate                                     |                                      |          | 0.1              |            | μV/μs                |  |

| S/H Acquisition Time                               |                                      |          | 0.5              |            | μs                   |  |

| S/H Aperture Delay                                 |                                      |          | 50<br>50         |            | ns                   |  |

| S/H Aperture Jitter                                |                                      |          | 50               |            | ps                   |  |

| Sampling Skew, Channel-to-Channel                  |                                      |          | 3                |            | ns                   |  |

| DC ACCURACY                                        |                                      |          | 10.5             | 10         | 1.00                 |  |

| Integral Linearity - ADC                           |                                      |          | ±0.5             | ±2         | LSB                  |  |

| Differential Linearity - ADC                       |                                      | 40       | ±0.5             | ±2         | LSB                  |  |

| No Missing Codes                                   |                                      | 12       | 0.5              | 10         | Bits                 |  |

| Integral Linearity - Asynchronous, Synchronous     |                                      |          | 0.5              | ±3         | LSB                  |  |

| Differential Linearity - Asynchronous, Synchronous | 0 10/0/                              |          | 0.5              | ±3<br>2    | LSB                  |  |

| Full Scale Error Full Scale Error Other Gains      | G = 1.0V/V                           |          |                  | 4          | % of FSR<br>% of FSR |  |

| Full Scale Error Drift                             | G = 1.0V/V                           |          | ±10              | ±100       | ppm/°C               |  |

| Full Scale Life Dilit                              | G = 1.0V/V<br>G = 2.5V/V             |          | ±10              | ±100       | ppm/°C               |  |

| Zero Error - ADC                                   | G = 2.5V/V<br>G = 1.0V/V             |          | ±0.5             | ±15        | LSB                  |  |

| Zero Error - Asynchronous, Synchronous             | G = 1.0V/V<br>G = 1.0V/V             |          | ±0.5             | ±15<br>±20 | LSB                  |  |

| Zero Error Drift                                   | G = 1.0V/V                           |          | ±0.5             | 120        | ppm/°C               |  |

| AC ACCURACY                                        | G = 1.0V/V                           |          | ±0.0             |            | ррпі/ О              |  |

| Total Harmonic Distortion                          |                                      |          |                  |            |                      |  |

| f <sub>IN</sub> = 1kHz                             |                                      |          | 92               |            | dB                   |  |

| $f_{IN} = 1MHz$                                    |                                      |          | 70               |            | dB                   |  |

| CMR                                                | $V_{CM} = \pm 0.5 V, f_{CM} = 1 MHz$ |          | 50               |            | dB                   |  |

| REFERENCE                                          | GIVI , GIVI                          |          |                  |            |                      |  |

| Internal Reference Voltage                         |                                      |          | 2.5              |            | l v                  |  |

| Internal Reference Accuracy                        |                                      |          | ±0.25            | ±2         | %                    |  |

| Internal Reference Drift                           |                                      |          | ±10              |            | ppm/°C               |  |

| Internal Reference Source Current                  |                                      |          | 10               |            | μΑ                   |  |

| External Reference Voltage Range                   |                                      | 2.25     | 2.5              | 2.75       | ·v                   |  |

| for Specified Linearity                            |                                      |          |                  |            |                      |  |

| External Reference Current Drain                   |                                      |          | 10               |            | μΑ                   |  |

| DIGITAL INPUTS                                     |                                      |          |                  |            |                      |  |

| Logic Levels                                       |                                      |          |                  |            |                      |  |

| $V_{IL}$                                           |                                      | 0        |                  | 1.5        | V                    |  |

| $V_{IH}$                                           |                                      | +3.5     |                  | +5         | V                    |  |

| $I_{lL}$                                           |                                      |          |                  | ±10        | μΑ                   |  |

| I <sub>IH</sub>                                    | At All Digital Inner Die-            |          |                  | ±10        | μA                   |  |

| Input Capacitance                                  | At All Digital Input Pins            |          |                  | 15         | pF                   |  |

| DIGITAL OUTPUTS                                    |                                      |          | 40 Bit 0i-/      |            |                      |  |

| Data Format                                        |                                      |          | 12-Bit Serial    |            |                      |  |

| Data Coding                                        | 404                                  | •        | BTC              | 0.4        |                      |  |

| V <sub>OL</sub>                                    | I <sub>SINK</sub> = 1.6mA            | 0<br>4.2 |                  | 0.4        | V<br>V               |  |

| V <sub>OH</sub>                                    | I <sub>SOURCE</sub> = 500μA          | 4.2      |                  | 5          | 1                    |  |

| Leakage Current                                    | At All Digital Costs of Dis          |          |                  | ±5         | μA                   |  |

| Output Capacitance                                 | At All Digital Output Pins           |          |                  | 15         | pF                   |  |

## **SPECIFICATIONS** (Cont.)

At  $V_{ANA+}$  = +5V,  $V_{ANA-}$  = -5V,  $V_{DIG+}$  = +5V,  $V_{DIG-}$  = -5V, and  $T_A$  = -40°C to +85°C, using internal reference,  $f_{CLOCK}$  = 1.25MHz.

#### **ANALOG-TO-DIGITAL CONVERTER CHANNELS**

|                       |                       |       |      | VECANA01N |       |  |

|-----------------------|-----------------------|-------|------|-----------|-------|--|

| PARAMETER             | CONDITIONS            | MIN   | TYP  | MAX       | UNITS |  |

| POWER SUPPLIES        | Specified Performance |       |      |           |       |  |

| $V_{ANA+}$            |                       | +4.75 | +5.0 | +5.25     | V     |  |

| $V_{ANA-}$            |                       | -4.75 | -5.0 | -5.25     | V     |  |

| V <sub>DIG+</sub>     |                       | +4.75 | +5.0 | +5.25     | V     |  |

| V <sub>DIG</sub>      |                       | -4.75 | -5.0 | -5.25     | V     |  |

| I <sub>ANA+</sub>     |                       |       | 15   |           | mA    |  |

| I <sub>ANA</sub>      |                       |       | -8   |           | mA    |  |

| I <sub>DIG+</sub>     |                       |       | 12   |           | mA    |  |

| I <sub>DIG</sub>      |                       |       | -10  |           | mA    |  |

| Power Dissipation     |                       |       | 225  |           | mW    |  |

| TEMPERATURE RANGE     |                       |       |      |           |       |  |

| Specified Performance |                       | -40   |      | +85       | °C    |  |

| Derated Performance   |                       | -55   |      | +125      | °C    |  |

| Storage               |                       | -65   |      | +150      | °C    |  |

#### **DIGITAL-TO-ANALOG CONVERTER**

|                                  |            |        | VECANA01N |      |       |

|----------------------------------|------------|--------|-----------|------|-------|

| PARAMETER                        | CONDITIONS | MIN    | TYP       | MAX  | UNITS |

| RESOLUTION                       |            | 8-Bits |           |      |       |

| Output Range                     |            | 0      |           | +2.5 | V     |

| Output Settling Time             | 0.5LSB     |        | 0.2       | 1    | μs    |

| Linearity Error                  |            |        |           | ±1   | LSB   |

| Differential Linearity           |            |        |           | ±1   | LSB   |

| Output Current                   |            | 200    |           |      | μΑ    |

| Offset Error                     |            |        | ±1        | ±10  | mV    |

| Full Scale Error (including REF) |            |        |           | ±2   | %     |

#### SIGN AND WINDOW COMPARATORS

| PARAMETER                                                                                                                                                                                                              | CONDITIONS | MIN | TYP                         | MAX                            | UNITS                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----------------------------|--------------------------------|----------------------|

| Differential Input Voltage Range of the Window Comparators                                                                                                                                                             |            |     |                             | ±2.5                           | V                    |

| Offset Error of the Window Comparators Hysteresis of the Window Comparators Offset Error of the Sign Current Comparators Hysteresis of the Sign Current Comparators Offset Error of the Sign Sensor Signal Comparators |            |     | ±20<br>60<br>±5<br>10<br>±5 | ±80<br>100<br>±20<br>30<br>±30 | mV<br>mV<br>mV<br>mV |

| Hysteresis of the Sign Sensor Signal Comparators                                                                                                                                                                       |            |     | 75                          | 90                             | mV                   |

| Absolute Input Range of the Comparators<br>Delay Time of the Sign Comparators<br>Delay Time of the Window Comparators                                                                                                  |            |     | ±2.9<br>25<br>250           | ±3.2<br>150<br>1500            | V<br>ns<br>ns        |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

#### **ABSOLUTE MAXIMUM RATINGS**

| Ground Voltage Difference: AGND and DGND Power Supply Voltages: | ±0.3V                          |

|-----------------------------------------------------------------|--------------------------------|

| V <sub>ANA+</sub>                                               | +7V                            |

| V <sub>ANA-</sub>                                               | 7V                             |

| V <sub>DIG+</sub>                                               | +7V                            |

| V <sub>DIG-</sub>                                               | 7V                             |

| Digital Inputs                                                  | 0.3V to V <sub>DIG</sub> +0.3V |

| Maximum Junction Temperature                                    | +165°C                         |

| Internal Power Dissipation                                      | 825mW                          |

| Lead Temperature (soldering, 10s)                               | +300°C                         |

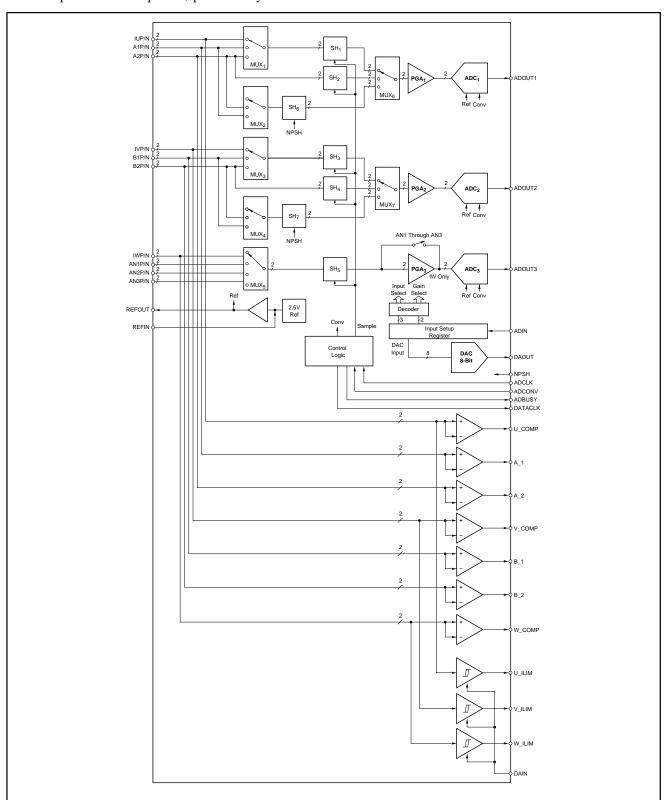

#### **CONVERSION AND DATA TIMING**

| SYMBOL            | DESCRIPTION                                              | MIN  | TYP | MAX | UNITS |

|-------------------|----------------------------------------------------------|------|-----|-----|-------|

| t <sub>CONV</sub> | A/D Conversion Time                                      | 10.4 | 6.2 |     | μs    |

| CLK               | A/D Conversion Clock                                     | 1.25 | 2.1 |     | MHz   |

| t <sub>1</sub>    | Setup Time for Conversion<br>Before Rising Edge of Clock | 50   |     |     | ns    |

| t <sub>2</sub>    | Hold Time for Conversion<br>After Rising Edge of Clock   | 50   |     |     | ns    |

| t <sub>3</sub>    | Setup Time for Serial Out                                |      | 125 |     | ns    |

| t <sub>4</sub>    | Setup Time for Serial Input                              | 30   |     |     | ns    |

| t <sub>5</sub>    | Hold Time for Serial Input                               | 30   |     |     | ns    |

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT  | PACKAGE | PACKAGE<br>DRAWING<br>NUMBER | SPECIFIED<br>TEMPERATURE<br>RANGE | PACKAGE<br>MARKING | ORDERING<br>NUMBER | TRANSPORT<br>MEDIA |

|----------|---------|------------------------------|-----------------------------------|--------------------|--------------------|--------------------|

| VECANA01 | PLCC-68 | 312                          | -40°C to +85°C                    | VECANA01           | VECANA01           | Rails              |

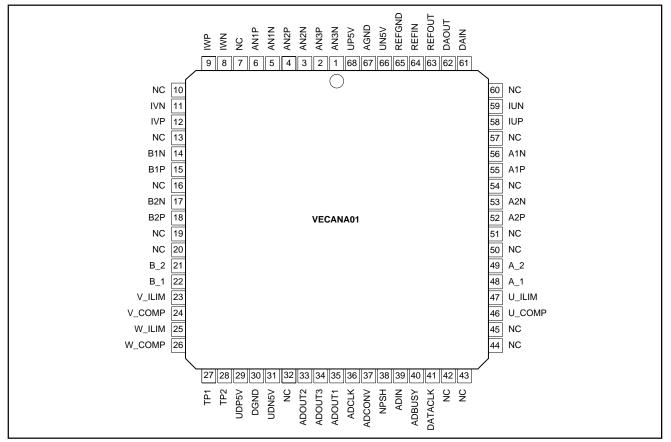

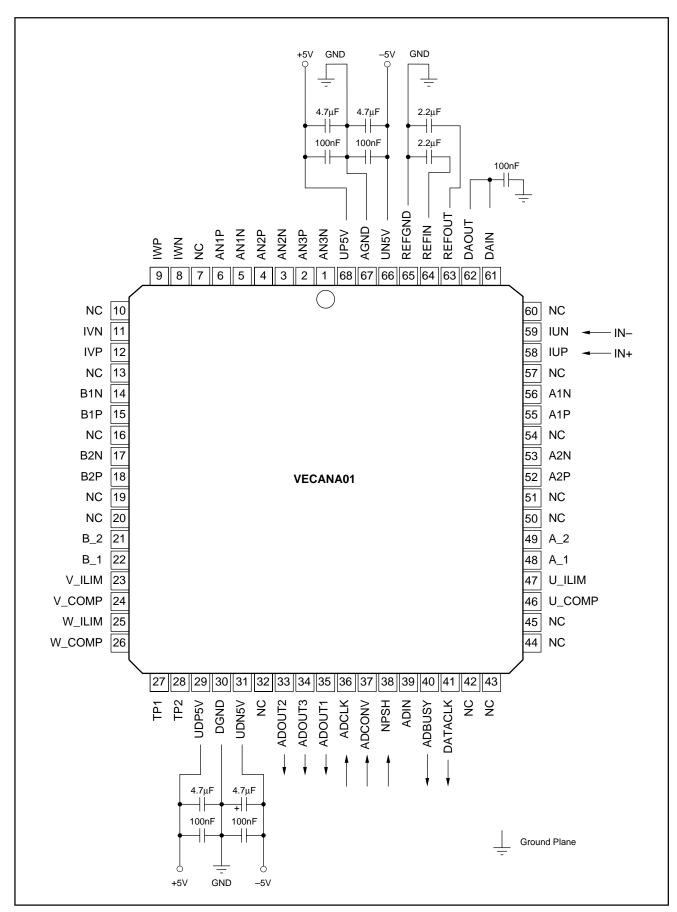

#### **PIN CONFIGURATION**

#### **PIN DEFINITIONS**

| PIN NO | NAME       | TYPE(1) | DESCRIPTION                                                                                                                                        | PIN NO | NAME     | TYPE(1) | DESCRIPTION                                                                                                                                        |

|--------|------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|--------|----------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | AN3N       | Al      | Auxiliary analog input channel 3, Negative Side                                                                                                    | 36     | ADCLK    | DI      | Clock for the A/D converters. The nominal clock                                                                                                    |

| 2      | AN3P       | Al      | Auxiliary analog input channel 3, Positive Side                                                                                                    |        |          |         | frequency is 1.25MHz.                                                                                                                              |

| 3      | AN2N       | Al      | Auxiliary analog input channel 2, Negative Side                                                                                                    | 37     | ADCONV   | DI      | Start signal for the A/D converter, active low. The                                                                                                |

| 4      | AN2P       | Al      | Auxiliary analog input channel 2, Positive Side                                                                                                    |        |          |         | first rising clock edge of ADCLK, when ADCONV                                                                                                      |

| 5      | AN1N       | Al      | Auxiliary analog input channel 1, Negative Side                                                                                                    | 20     | NDCH     | DI      | is 0, starts the conversion.                                                                                                                       |

| 6      | AN1P       | Al      | Auxiliary analog input channel 1, Positive Side                                                                                                    | 38     | NPSH     | DI      | Sample/hold control for sampling the position sensor signals. If the value is 1, the signals are                                                   |

| 7      | NC         | _       | No Connection                                                                                                                                      |        |          |         | sampled, if it is 0 they are stored.                                                                                                               |

| 8      | IWN        | Al      | Analog input of phase W current, Negative Side                                                                                                     | 39     | ADIN     | DI      | Serial input signal for programming the D/A                                                                                                        |

| 9      | IWP        | Al      | Analog input of phase W current, Positive Side                                                                                                     |        |          |         | converter for setting the limit value of the current                                                                                               |

| 10     | NC         | _       | No Connection                                                                                                                                      |        |          |         | signals for the input voltage range of the A/D                                                                                                     |

| 11     | IVN        | Al      | Analog input of phase V current, Negative Side                                                                                                     |        |          |         | converters and for the input multiplexer of the                                                                                                    |

| 12     | IVP        | Al      | Analog input of phase V current, Positive Side                                                                                                     | 40     | ADDITION | DO.     | A/D converters.                                                                                                                                    |

| 13     | NC         | _       | No Connection                                                                                                                                      | 40     | ADBUSY   | DO      | Conversion is executing, active low                                                                                                                |

| 14     | B1N        | Al      | Signal B analog input of position sensor 1,                                                                                                        | 41     | DATACLK  | _       | Test pin, do not connect to in normal operation.                                                                                                   |

|        |            |         | Negative Side                                                                                                                                      | 42     | NC       | _       | No Connection                                                                                                                                      |

| 15     | B1P        | Al      | Signal B analog input of position sensor 1,                                                                                                        | 43     | NC       | _       | No Connection                                                                                                                                      |

|        |            |         | Positive Side                                                                                                                                      | 44     | NC       | _       | No Connection                                                                                                                                      |

| 16     | NC         | _       | No Connection                                                                                                                                      | 45     | NC       | _       | No Connection                                                                                                                                      |

| 17     | B2N        | Al      | Signal B analog input of position sensor 2,<br>Negative Side                                                                                       | 46     | U_COMP   | DO      | Sign of phase U current signal (IUP, IUN). If the value is positive (IUP > IUN) U_COMP is 1, if the value is negative (IUP < IUN) U_COMP is 0.     |

| 18     | B2P        | Al      | Signal B analog input of position sensor 2, Positive Side                                                                                          | 47     | U_ILIM   | DO      | Over-current output of phase U, active low. If IUP-IUN is greater then the positive limiting value                                                 |

| 19     | NC         | _       | No Connection                                                                                                                                      |        |          |         | or less than the negative limiting value, U_ILIM                                                                                                   |

| 20     | NC<br>D. C | _       | No Connection                                                                                                                                      |        |          |         | becomes 0.                                                                                                                                         |

| 21     | B_2        | DO      | Sign of signal B position sensor 2 (B2P, B2N). If<br>the value is positive (B2P > B2N) B_2 is 1, if the<br>value is negative (B2P < B2N) B_2 is 0. | 48     | A_1      | DO      | Sign of signal A position sensor 1 (A1P, A1N). If<br>the value is positive (A1P > A1N) A_1 is 1, if the<br>value is negative (A1P < A1N) A_1 is 0. |

| 22     | B_1        | DO      | Sign of signal B position sensor 1 (B1P, B1N). If<br>the value is positive (B1P > B1N) B_1 is 1, if the<br>value is negative (B1P < B1N) B_1 is 0. | 49     | A_2      | DO      | Sign of signal A position sensor 2 (A2P, A2N). If<br>the value is positive (A2P > A2N) A_2 is 1, if the<br>value is negative (A2P < A2N) A_2 is 0. |

| 23     | V_ILIM     | DO      | Over-current output of phase V, active low. If                                                                                                     | 50     | NC       | _       | No Connection                                                                                                                                      |

|        | _          |         | IVP-IVN is greater then the positive limiting value                                                                                                | 51     | NC<br>NC | _       | No Connection                                                                                                                                      |

|        |            |         | or less than the negative limiting value, U_ILIM becomes 0.                                                                                        | 52     | A2P      | AI      | Signal A analog input of position sensor 2, Negative Side                                                                                          |

| 24     | V_COMP     | DO      | Sign of phase V current signal (IVP, IVN). If the value is positive (IVP > IVN) V_COMP is 1, if the value is negative (IVP < IVN) V_COMP is 0.     | 53     | A2N      | AI      | Signal A analog input of position sensor 2, Positive Side                                                                                          |

| 25     | W_ILIM     | DO      | Over-current output of phase W, active low. If                                                                                                     | 54     | NC       | _       | No Connection                                                                                                                                      |

| 25     | VV_IEIW    |         | IWP-IWN is greater then the positive limiting value or less than the negative limiting value,                                                      | 55     | A1P      | AI      | Signal A analog input of position sensor 1, Positive Side                                                                                          |

| 26     | W_COMP     | DO      | U_ILIM becomes 0. Sign of phase W current signal (IWP, IWN). If                                                                                    | 56     | A1N      | Al      | Signal A analog input of position sensor 1,<br>Negative Side                                                                                       |

|        |            |         | the value is positive (IWP > IWN) W_COMP is 1,                                                                                                     | 57     | NC       | -       | No Connection                                                                                                                                      |

|        |            |         | if the value is negative (IWP < IWN) W_COMP                                                                                                        | 58     | IUP      | Al      | Analog input of phase U current, Positive Side                                                                                                     |

|        |            |         | is 0.                                                                                                                                              | 59     | IUN      | Al      | Analog input of phase U current, Negative Side                                                                                                     |

| 27     | TP1        | _       | Test pin, do not connect to in normal operation.                                                                                                   | 60     | NC       | _       | No Connection                                                                                                                                      |

| 28     | TP2        | _       | Test pin, do not connect to in normal operation.                                                                                                   | 61     | DAIN     | Al      | Input for setting the over-current value. Normally                                                                                                 |

| 29     | UDP5V      | P       | Digital Supply Voltage, +5V                                                                                                                        |        |          |         | connected to DAOUT                                                                                                                                 |

| 30     | DGND       | P       | Digital Supply Voltage, Ground                                                                                                                     | 62     | DAOUT    | AO      | Output of the D/A converter for programming the                                                                                                    |

| 31     | UDN5V      | Р       | Digital Supply Voltage, –5V                                                                                                                        |        |          |         | over-current limit. Output is programmable from                                                                                                    |

| 32     | NC         | _       | No Connection                                                                                                                                      |        | DEFOUT   |         | OV to +2.5V.                                                                                                                                       |

| 33     | ADOUT2     | DO      | Serial output signal of A/D converter 2. Rising clock edges of ADCLK outputs the bits of the                                                       | 63     | REFOUT   | AO      | Output pin of the integrated reference source, nominal voltage 2.5V.                                                                               |

| 24     | ADOUTO     | D0      | A/D converter with MSB first.                                                                                                                      | 64     | REFIN    | Al      | Input pin for an external reference voltage.                                                                                                       |

| 34     | ADOUT3     | DO      | Serial output signal of A/D converter 3. Rising clock edges of ADCLK outputs the bits of the                                                       | 65     | REFGND   | P       | Ground pin of the reference source.                                                                                                                |

|        |            |         | A/D converter with MSB first.                                                                                                                      | 66     | UN5V     | P       | Analog Supply Voltage, –5V                                                                                                                         |

| 35     | ADOUT1     | DO      | Serial output signal of A/D converter 1. Rising                                                                                                    | 67     | AGND     | P       | Analog Supply Voltage, Ground                                                                                                                      |

|        |            | _       | clock edges of ADCLK outputs the bits of the A/D converter with MSB first.                                                                         | 68     | UP5V     | P       | Analog Supply Voltage, +5V                                                                                                                         |

$NOTE: (1) \ AI \ is \ Analog \ Input, \ AO \ is \ Analog \ Output, \ DI \ is \ Digital \ Input, \ DO \ is \ Digital \ Output, \ P \ is \ Power \ Supply \ Connection.$

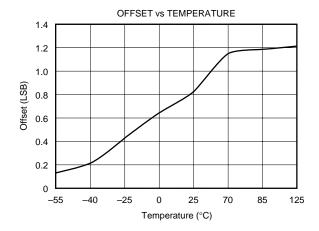

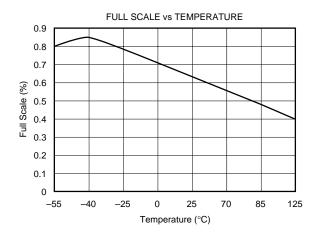

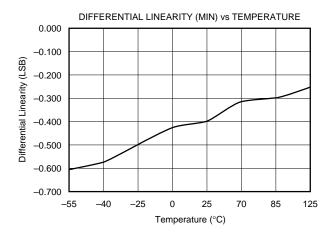

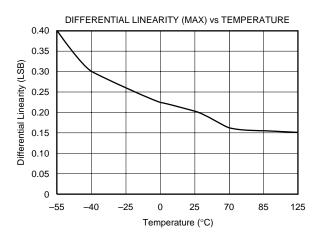

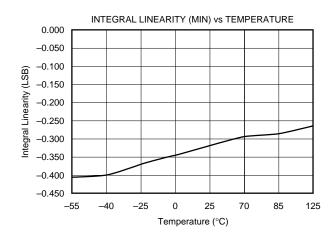

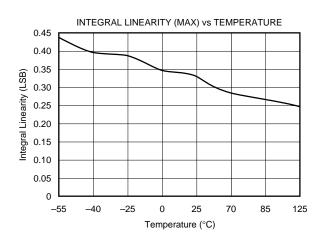

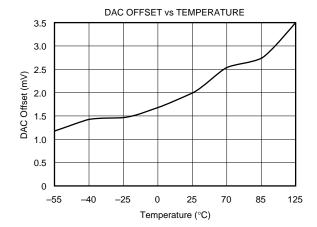

### TYPICAL PERFORMANCE CURVES

At  $V_{ANA+}$  = +5V,  $V_{ANA-}$  = -5V,  $V_{DIG+}$  = +5V,  $V_{DIG-}$  = -5V and  $T_A$  = 25°C, using internal reference,  $f_{CLOCK}$  = 1.25MHz.

## **TYPICAL PERFORMANCE CURVES (Cont.)**

At  $V_{ANA+}$  = +5V,  $V_{ANA-}$  = -5V,  $V_{DIG+}$  = +5V,  $V_{DIG-}$  = -5V and  $T_A$  = 25°C, using internal reference,  $f_{CLOCK}$  = 1.25MHz.

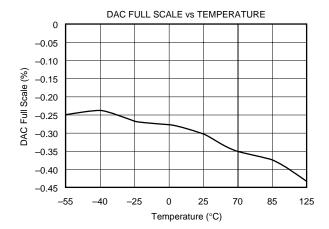

### **FUNCTIONAL DESCRIPTION**

The VECAN01 is a triple 12-bit SAR A/D converter that operates from dual ±5V power supplies. The part contains three 12-bit successive approximation ADCs, multiplexer for 10 fully differential inputs, 5 differential input synchronized sample-and-hold amplifiers, plus two asynchronous

sample-and-hold amplifier. It communicates over three synchronous SPI/SSI serial output and one input ports. The VECANA01 operates on external clock that also determines the output data rate (see Figure 2).

FIGURE 1. Functional Diagram.

#### **MULTIPLEXERS**

The VECANA01 has several input multiplexers that are used to select the desired analog inputs and connect the proper sample-and-hold outputs to the PGAs and A/D converters. A decoder receives its inputs from the Input Setup Register and drives the MUXs (see Table VII and Table VIII for information on selecting the input channel). The input multiplexers can take full differential or single-ended signals (see Figure 4 and Table III). The analog signals stay differential through the sample holds and the PGAs all the way to the inputs of the A/D converter. This provides the best possible noise rejection.

#### **SAMPLE-AND-HOLD**

The VECANA01 contains seven sample-and-hold amplifiers. Five of them (SH $_1$  through SH $_5$ ) sample simultaneously and have their sample-and-hold timing internally synchronized (the timing is shown in Figure 2). Three of the sample-and-holds (SH $_1$ , SH $_3$ , and SH $_5$ ) are connected to the input multiplexers so that they can provide simultaneous sampling for all of their channel inputs. In addition, SH $_2$  and SH $_4$  simultaneously sample the third input of their channel (A2 and B2, respectively). This is useful in motor control applications where A1 and B1 are the quadrature inputs for one position sensor, and A2 and B2 are the quadrature inputs for a second position sensor (see Figure 9). In that application, it is desir-

able to sample the quadrature inputs of a given position sensor at the same time (even though they are converted on successive conversion cycles) (see Table VII), so that their values are captured at the same shaft position. The VECANA01 also has the capability for limited asynchronous sampling. The sampling of  $SH_6$  and  $SH_7$  is controlled asynchronously by the control signal NPSH (see Table VII). This allows two inputs, each on Channel 1 and Channel 2 (see Table VIII) to be sampled asynchronously from the timing of the other sample holds. This can be useful in motor control applications where the two inputs for each channel need to be sampled asynchronously to a reference point.

#### **ADCS AND PGAS**

The VECANA01 contains three signal channels each with a 12-bit A/D converter output. The A/D converters operate synchronously and their serial outputs occur simultaneously (Table IX gives the analog input/digital output relationships). Programmable gain amplifiers precede the A/D converters (Table IX gives gain select information). For channels one and two, the PGAs are effective for all three analog inputs. For the third channel, only the IW input is gain changed by the PGA. Inputs AN1, AN2, and AN3 are connected to the A/D converter three at a fixed gain of 1.0V/V regardless of the gain select value.

FIGURE 2. Timing Diagram.

#### **VOLTAGE REFERENCE**

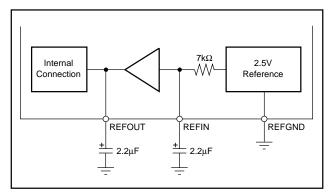

The VECANA01 contains an internal 2.5V voltage reference. It is available externally through an output buffer amplifier. If it is desired to use an external reference, one may be connected at the REFIN pin. The output resistance of this pin for the external reference voltage is typically  $7k\Omega$ . This then overrides the internal 2.5V reference and is connected to the A/D converter. It is also available as a buffered output at the REFOUT pin.

The reference voltage shall be buffered by an external capacitor (approx.  $2.2\mu F$ ) on the REFIN pin and also on the REFOUT pin (see Figure 3), as close as possible to the pin.

FIGURE 3. Reference Voltage Connection.

#### **DIGITAL-TO-ANALOG CONVERTER**

An 8-bit DAC provides 256 output voltage levels from 0V to 2.499V (see Table I for input/output relationships). The DAC is controlled by the DAC Input portion of the input setup word. The DAC Input portion of the word is strobed into the DAC at the end of the conversion cycle (14th CLK pulse in Figure 2).

| DIGITAI<br>DAC IN                  | ANALOG OUTPUT          |                |

|------------------------------------|------------------------|----------------|

| HEX<br>CODE                        | BINARY<br>CODE         |                |

| 00 <sub>H</sub><br>01 <sub>H</sub> | 0000 0000<br>0000 0001 | 0V<br>+0.0098V |

| :                                  |                        | •              |

| FF <sub>H</sub>                    | •<br>1111 1111         | •<br>+2.499    |

TABLE I. DAC Input/Output Relationships.

#### DAC OUTPUT VOLTAGE

The value of the DAC output voltage is determined by the DAC Input portion of the ADIN word (bits 0 through 7, see Figure 2). The 8-bit DAC has 256 possible output steps from 0V to +2.499V. The value of 1LSB is 0.0098V.

#### OTHER DIGITAL INPUTS AND OUTPUTS

Sampling and conversion is controlled by the ADCONV and ADCLK input (see Figure 2). The VECANA01 is designed to operate from an external clock supplied at the ADCLK

input. This allows the conversion to be synchronous with system timing so that transient noise effects can be minimized. The ADCLK signal may run continuously or may be supplied only during convert sequences. The ADBUSY and DATACLK signals are internally generated and are supplied to make interfaces with microprocessors easier (see Figures 2 and 9).

#### POWER-UP INITIALIZATION

When power is applied to the VECANA01, two conversion cycles are required for initialization before valid digital data is transmitted on the third cycle. The first conversion, after power is applied, is performed with indeterminate configuration values in the double buffer output of the Input Setup Register. The second conversion cycle loads the desired values into the register. The third conversion uses those values to perform proper conversions and output valid digital data from each of the A/D converters.

| CLOCK<br>POSITIONS <sup>(1)</sup>                                    | DESCRIPTION                | FUNCTIONS               |  |  |

|----------------------------------------------------------------------|----------------------------|-------------------------|--|--|

| 2-9                                                                  | DAC Input <sub>0-7</sub>   | Sets DAC Output Voltage |  |  |

| 10-11                                                                | Gain Select <sub>0-1</sub> | Sets PGA Gains          |  |  |

| 12-14 Input Select <sub>0-2</sub> Determines Multiplexers Conditions |                            |                         |  |  |

| NOTE: (1) See Figure 2, "Clock Pulse Reference No."                  |                            |                         |  |  |

TABLE II. Description of Configurable Parameters.

#### **CONFIGURABLE PARAMETERS**

Configurable parameters are:

- PGA Gain

- Input Multiplexer and Sample-and-Hold Selection

- DAC Output Voltage

Configuration information for these parameters is contained in the ADIN word (see Figure 2). As one conversion is taking place, the configuration for the next conversion is being loaded into the buffered Input Setup Register via the ADIN word. Tables I, VII, VIII and X shows information regarding these parameters.

## ANALOG-TO-DIGITAL CONVERTERS

#### **ARCHITECTURE**

The A/D converters are 12-bit, successive approximation types implemented with a switched capacitor circuitry.

#### **CLOCK RATE**

The clock for the A/D converter conversion is supplied externally at the ADCLK pin. Typical clock frequency for specified accuracy is 1.25MHz. This results in a complete conversion cycle (S/H acquisition and A/D conversion) of 10.4 µs

#### INPUT/OUTPUT

The VECANA01 is designed for bipolar input voltages and uses a binary two's complement digital output code. A programmable gain function is associated with each A/D converter. This changes the full-scale analog input range and the analog resolution of the converter. Details are shown in Table IX.

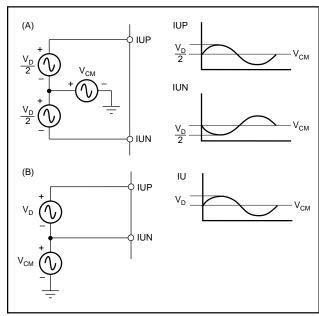

## DIFFERENTIAL AND COMMON-MODE INPUT VOLTAGES

The VECANA01 is designed with full differential signal paths all the way from the multiplexer inputs through to the input of the A/D converters. This was done to provide superior high frequency noise rejection. As is common with most differential input semiconductor devices, there are compound restrictions on the combination of differential and common-mode input voltages. This matter is made slightly more complicated by the fact that most of the analog inputs are capable of being affected by the programmable gain function. The possible differential and single-ended configurations are shown in Figures 4a and 4b. The maximum differential and common-mode restrictions are shown in Table III.

| GAIN SELECT CODE                                              | 0      | 1      | 2       | 3      |

|---------------------------------------------------------------|--------|--------|---------|--------|

| Gain                                                          | 5.0V/V | 2.5V/V | 1.25V/V | 1.0V/V |

| Full Scale Range (V <sub>D</sub> with V <sub>CM</sub> = 0)    | ±0.5V  | ±1.0V  | ±2.0V   | ±2.5V  |

| Largest Positive<br>Common Mode<br>Voltage, V <sub>CM</sub> + | +2.7V  | +2.4V  | +1.9V   | +1.6V  |

| Largest Negative<br>Common Mode<br>Voltage, V <sub>CM</sub> - | -2.7V  | -2.4V  | -1.9V   | -1.6V  |

TABLE III. Differential and Common Mode Voltage Restrictions.

FIGURE 4. (a) Differential Signal Source. (b) Single-ended Input.

#### **INPUT SETUP**

As the A/D converters are converting and transmitting their serial digital data for one conversion cycle, a setup word is received to be used for the next conversion cycle. The 13-bit word is supplied at the ADIN pin (see Figure 1), and is stored in the buffered Input Setup Register. The Input Select and Gain Select portions of the word are decoded and determine the state of the multiplexers and PGAs (see CONFIGURABLE PARAMETERS section).

## INPUT MULTIPLEXER AND SAMPLE HOLD SELECTION

The Input Select portion of the ADIN word (bits 10, 11 and 12) (see Figure 2) are decoded and determine the open/closed condition of the multiplexer switches. This in turn determines which input signals are connected to the sample and holds and which sample and holds are connected to the PGAs/ADCs.

#### SIGN OF THE INPUT SIGNALS

The VECANA01 contains seven comparators, which acquire the signals of the first seven input analog signals. The digital outputs of the sign comparators are the signals X\_COMP. If the positive input value is greater than the negative input value, the X-COMP output becomes High (logic "1") or if the reverse, the X-COMP output is Low (logic "0"), (see Table IV).

| IUP – IUN | U_COMP |

|-----------|--------|

| A1P – A1N | A_1    |

| A2P – A2P | A_2    |

| IVP – IVN | V_COMP |

| B1P – B1N | B_1    |

| B2P – B2N | B_2    |

| IWP – IWN | W_COMP |

| > 0       | 1      |

| < 0       | 0      |

TABLE IV. Input - Output Relation.

The typical hysteresis value of comparators U\_COMP, V\_COMP and W\_COMP is 10mV. The typical hysteresis value of comparators A\_1, A\_2, B\_1, and B\_2 is 50mV. AC motor control applications will typically use 10mV hysteresis for phase current measurement and 50mV hysteresis for positioning sensor measurement.

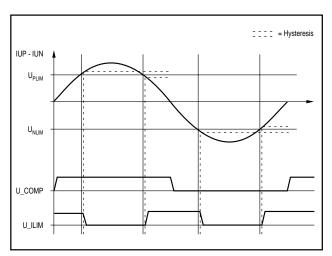

#### **OVER RANGE RECOGNITION**

The VECANA01 also includes three window comparators for the three input signals IU, IV and IW. Each window comparator is composed of two comparators that are monitoring the input value on the positive range limit ( $U_{PLIM}$ ) and negative range limit ( $U_{NLIM}$ ). The output values of the window comparators are output via the pins U\_ILIM, V\_ILIM and W\_ILIM. The two range limiting values are symmetrical to the zero point ( $U_{NLIM} = -U_{PLIM}$ ) and are determined by pin

DAIN. See Figure 5 for graphical view of the over limit set function (typically used for setting the current protection value), The DAIN value will determine the fixed range. Normally this pin is connected to DAOUT (the DAC output). In order to be able to program the range value through the control value DAC Input word, the DAC Input is an 8-bit wide unsigned value (controls the digital-to-analog converter output voltage (DAOUT)). This D/A converter has an output voltage range of 0V to 2.5V (see Table I).

| DAC INPUT | U <sub>PLIM</sub> | U <sub>NLIM</sub> |

|-----------|-------------------|-------------------|

| 0H        | 0V                | 0V                |

| 1H        | +0.0098V          | -0.0098V          |

| 2H        | +0.0195V          | -0.0195V          |

| 0FEH      | +2.4805V          | -2.4805V          |

| 0FFH      | +2.4902V          | -2.4902V          |

TABLE V. Over-Current Limit as a Function DAC Input.

If the input voltage exceeds the positive range limit (IXP – IXN >  $U_{PLIM}$ ) or it remains under the negative range (IXP – IXN <  $U_{NLIM}$ ), then the corresponding window comparator output is Low (logic "0") (U\_ILIM, V\_ILIM, or W\_ILIM). If the input value is within the limits, the comparator output is High (logic "1"). The input signal and output X\_ILIM signals are shown in Table VI.

| IUP – IUN                           | U_ILIM |

|-------------------------------------|--------|

| IVP – IVN                           | V_ILIM |

| IWP – IWN                           | W_ILIM |

| (IXP - IXN) > U <sub>PLIM</sub>     | 0      |

| $U_{PLIM} > (IXP - IXN) > U_{NLIM}$ | 1      |

| U <sub>NLIM</sub> > (IXP - IXN)     | 0      |

TABLE VI. The Limiting Value as Function of DAC Input.

The input voltage range of the comparators is the same as the A/D converter when the Gain Select is 3. The typical value of the hysteresis of the comparators is 50mV. Figure 5 shows the Logic State of the U\_COMP and U\_ILIM outputs for the input signal IVP – IUN. The output resistance of the D/A converter is approximately  $10k\Omega$ . The output voltage, DAOUT should be buffered by a capacitor of approximately 100nF (see Figure 6) The resulting time constant is approximately 1ms and typical does not disturb most applications.

#### **INPUT SIGNALS FOR PGAS/ADCS**

Table VII shows the relationships between the value of Input  $Select_{0-2}$  and the signals that are converted.

**Input Select = 7H**—Synchronously sample and convert input signals IU, IV, and IW.

FIGURE 5. Acquisition of the Current Sign and of the Over-Current.

| INPUT SELECT <sub>0-2</sub>             |        | ANALOG SIGNAL CONNECTED TO             |                                        |                                    |  |  |  |

|-----------------------------------------|--------|----------------------------------------|----------------------------------------|------------------------------------|--|--|--|

| HEX                                     | BINARY | PGA <sub>X</sub> /ADC <sub>X</sub>     |                                        |                                    |  |  |  |

| CODE                                    | CODE   | PGA <sub>1</sub> /ADC <sub>1</sub>     | PGA <sub>2</sub> /ADC <sub>2</sub>     | PGA <sub>3</sub> /ADC <sub>2</sub> |  |  |  |

| 0 <sub>H</sub>                          | 000    | Undefined                              | Undefined                              | AN3                                |  |  |  |

| 1 <sub>H</sub>                          | 001    | A_X via SH <sub>6</sub> <sup>(1)</sup> | B_X via SH <sub>7</sub> <sup>(1)</sup> | AN3                                |  |  |  |

| 2 <sub>H</sub>                          | 010    | A_2 via SH <sub>1</sub>                | B_2 via SH <sub>3</sub>                | AN2                                |  |  |  |

| 3 <sub>H</sub>                          | 011    | A_2 via SH <sub>2</sub>                | B_2 via SH <sub>4</sub>                | AN2                                |  |  |  |

| 4 <sub>H</sub>                          | 100    | A1                                     | B1                                     | AN1                                |  |  |  |

| 5 <sub>H</sub>                          | 101    | A1                                     | B1                                     | AN1                                |  |  |  |

| 6 <sub>H</sub>                          | 110    | A1                                     | B1                                     | AN1                                |  |  |  |

| 7 <sub>H</sub>                          | 111    | IU                                     | IV                                     | IW                                 |  |  |  |

| NOTE: (1) See Table VIII for Operation. |        |                                        |                                        |                                    |  |  |  |

TABLE VII. Input Controls for Synchronous Sample Holds.

**Input Select = 4H, 5H, 6H**—Synchronously sample and convert input signals A1, B1, and AN1. These codes also cause  $SH_2$  and  $SH_4$  to sample their inputs. Values  $4_H$ ,  $5_H$ ,  $6_H$  have different effects on the inputs to  $SH_6$  and  $SH_7$  (see Table VIII).

| INPUT          | SELECT <sub>0-2</sub> |                 |                 |  |  |

|----------------|-----------------------|-----------------|-----------------|--|--|

| HEX            | BINARY                | ANALOG SIGNAL   | CONNECTED TO    |  |  |

| CODE           | CODE                  | SH <sub>6</sub> | SH <sub>7</sub> |  |  |

| 0 <sub>H</sub> | 000                   | No Effect       | No Effect       |  |  |

| 1 <sub>H</sub> | 001                   | No Effect       | No Effect       |  |  |

| 2 <sub>H</sub> | 010                   | No Effect       | No Effect       |  |  |

| 3 <sub>H</sub> | 011                   | No Effect       | No Effect       |  |  |

| 4 <sub>H</sub> | 100                   | Open            | Open            |  |  |

| 5 <sub>H</sub> | 101                   | A1              | B1              |  |  |

| 6 <sub>H</sub> | 110                   | A2              | B2              |  |  |

| 7 <sub>H</sub> | 111                   | No Effect       | No Effect       |  |  |

TABLE VIII. Input Controls for Asynchronous Sample Holds.

**Input Select = 3H**—Convert A2 via SH<sub>2</sub>, B2 via SH<sub>4</sub>, and AN2 (A2 and B2 are from the value sampled in a preceding conversion cycle with Input Select =  $4_{\rm H}$ ,  $5_{\rm H}$  or  $6_{\rm H}$ ).

**Input Select = 2H** —Convert A2 via  $SH_1$ , B2 via  $SH_3$ , and AN2.

FIGURE 6. Basic Circuit Configuration.

| DESCRIPTION                                                                                  |                                                  | ANALO                                             | G INPUT                                          | DIGITAL OUTPUT                                |                                                                                      |                                                                                        |  |

|----------------------------------------------------------------------------------------------|--------------------------------------------------|---------------------------------------------------|--------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|--|

| GAIN SELECT CODE                                                                             | 0                                                | 1                                                 | 2                                                | 3                                             |                                                                                      |                                                                                        |  |

| GAIN                                                                                         | 5V/V                                             | 2.5V/V                                            | V/V 1.25V/V                                      | 1.0V/V BINARY TWO'S COMF                      |                                                                                      | IPLIMENT FORMAT                                                                        |  |

| FULL SCALE RANGE                                                                             | ±0.5V ±1.0V                                      |                                                   | ±2.0V                                            | ±2.5V HEX CODE BINA                           |                                                                                      | BINARY CODE                                                                            |  |

| +Full Scale (FS -1LSB) One Bit above Mid-Scale Mid-Scale One Bit Below Mid-Scale -Full Scale | +0.49976<br>+0.244mV<br>0V<br>-0.244V<br>-0.500V | +0.9995V<br>+0.488mV<br>0V<br>-0.488mV<br>-1.000V | +1.999V<br>+0.976mV<br>0V<br>-0.976mV<br>-2.000V | +2.499<br>+1.22mV<br>0V<br>-1.22mV<br>-2.500V | 7FF <sub>H</sub><br>001H<br>000 <sub>H</sub><br>FFF <sub>H</sub><br>800 <sub>H</sub> | 0111 1111 1111<br>0000 0000 0001<br>0000 0000 0000<br>1111 1111 1111<br>1000 0000 0000 |  |

NOTE: The programmable gain function applies to all three input channels for  $ADC_1$  and  $ADC_2$ . However, the programmable gain function only applies to the first input (IW) for  $ADC_3$ . The other three inputs (AN1, AN2, and AN3) are not affected by the GAIN SEL input. They operate at a fixed gain of 1V/V and thus have a fixed  $\pm 2.5$ V full scale input range.

TABLE IX. Analog Input - Digital Output Relationships.

**Input Select = 1H**—Input AN3 is converted by ADC<sub>3</sub>. The output of the asynchronous sample holds,  $SH_6$  and  $SH_7$ , are converted by  $PGA_1/ADC_1$  and  $PGA_2/ADC_2$ , respectively. Note that the inputs to  $SH_6$  and  $SH_7$  are determined by previous Input Select values (see Table VIII). Thus, to properly convert the output of one of the asynchronous sample holds it is first necessary to choose its input with a previous conversion cycle. Also, the output of  $SH_6$  or  $SH_7$  will only be converted if NPSH goes low before the ADCONV command is received.

**Input Select = 0 H**—AN3 is converted by ADC<sub>3</sub>. The inputs to  $PGA_1/ADC_1$  and  $PGA_2/ADC_2$  are undefined.

#### **PGA GAIN**

The PGA gain is determined by the Gain Select portion (bits 8 and 9) in the ADIN word (see Figure 2). There is one gain input that sets the same gain for all three PGAs. The gain values and allowable full-scale inputs are shown in Table X.

| GAIN<br>SELECT <sub>0-1</sub> | GAIN<br>SETTING | FULL SCALE<br>INPUT |  |

|-------------------------------|-----------------|---------------------|--|

| 0 <sub>H</sub>                | 5.0V/V          | ±0.5V               |  |

| 1 <sub>H</sub>                | 2.5V/V          | ±1.0V               |  |

| 2 <sub>H</sub>                | 1.25V/V         | ±2.0V               |  |

| 3 <sub>H</sub>                | 1.0V/V          | ±2.5V               |  |

TABLE X. Gain Select Information.

For channels one and two the PGAs set the gain for all three analog inputs. For the third channel, only the IW input is gain changed by the PGA. Inputs AN1, AN2, and AN3 are connected to A/D converter three at a fixed gain of 1.0V/V regardless of the Gain Select value.

## CONVERSIONS FROM THE ASYNCHRONOUS SAMPLE HOLDS

Decoding the Input Select value also determines which inputs are applied to the two asynchronously controlled sample holds (SH<sub>6</sub> and SH<sub>7</sub>) (see Table VIII.) One of the three possible inputs is selected by the Input Select value

being 4, 5, or 6. The "No Effect" states indicate that these values of Input Select have no effect on the multiplexers at the input of  $SH_6$  and  $SH_7$ . When one of the "No Effect" values of Input Select is presented, the multiplexers will not be changed (i.e., their condition is determined by the last 4, 5, or 6 value of Input Select that existed prior to the "No Effect" state). Note that Input Select =  $1_H$  presents the output of  $SH_6$  and  $SH_7$  to  $PGA_1/ADC_1$  and  $PGA_2/ADC_2$ , respectively (see Table VII). Therefore, in order to properly convert the asynchronous sampled signals, it is first necessary to choose an input signal (Input Select equal 5 or 6 in Table VIII) with one load/convert cycle and then convert the sample hold output (Input Select = 4 in Table VII) in a following conversion cycle.

#### **POWER SUPPLY**

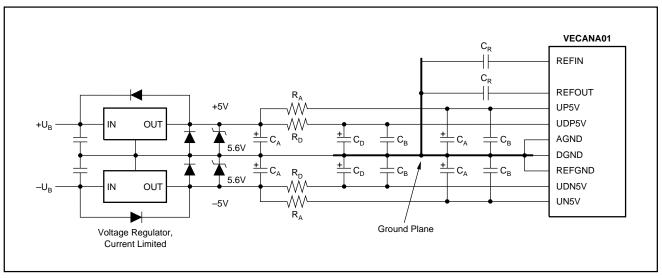

The VECANA01 requires an analog and digital supply voltage of  $\pm 5$ V. The substrate is connected to UP5V. The voltage difference between the analog and digital supply pin is not allowed to exceed a maximal value of 300mV. For this reason the circuit shown in Figure 7 is recommended for the power supply. The analog and digital power supplies are driven by a common source. Intermediate resistors provide for decoupling. Local current-limited voltage regulators generate the  $\pm 5$ V from the analog supply voltages  $\pm U_B$ . This guarantees a further noise reduction. The diodes are responsible for protecting the regulation and prevent polarity inversion. The zener diode protects against over-voltage possible from over-voltages to the analog inputs. Typical values for the resistors and capacitors are:

- $R_A \approx 3\Omega$

- $R_D \approx 3\Omega$

- $C_D \approx 22 \mu F$

- $C_A \approx 22 \mu F$

- $C_R \approx 100 nF$

- $C_R \approx 2.2 \mu F$

FIGURE 7. Power Supply of VECANA01.

#### **CONNECTION BETWEEN VECANA01 AND DSP**

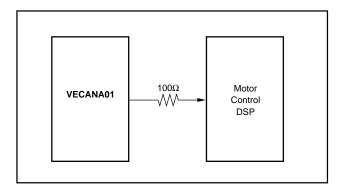

The interface between the VECANA01 and dSMC101 comprises the control signals for the A/D converters (ADCLK, ADCONV, ADIN, ADOUT1-3, NPSH, ADBUSY and DATACLK) and the comparator signals (X\_COMP and X\_ILIM). The signal levels and the driver capacity of the two chips are compatible. In order to avoid noise injection of the digital power supply into the analog VECANA01 chip, it is recommended to damp all digital lines with an intermediate resistor of approximately  $100\Omega$  as near as possible to the analog chip.

FIGURE 8. Damping of All Digital Lines.

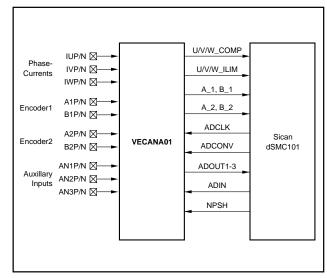

#### SICAN dSMC101 INTERFACE

The internal logic of the VECANA01 is designed for easy control and data interface with DSPs. Figure 9 shows the interface for loading the input control word from the DSP data bus into the serial input of the VECANA01.

FIGURE 9. DSP Interface for Sican dSMC101.

#### PACKAGE OPTION ADDENDUM

6-Nov-2006

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins I | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|--------|----------------|---------------------------|------------------|------------------------------|

| VECANA01         | NRND                  | PLCC            | FN                 | 68     | 20             | Green (RoHS & no Sb/Br)   | CU SN            | Level-3-260C-168 HR          |

| VECANA01G3       | ACTIVE                | PLCC            | FN                 | 68     | 20             | Green (RoHS & no Sb/Br)   | CU SN            | Level-3-260C-168 HR          |

(1) The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products           |                        | Applications       |                           |  |

|--------------------|------------------------|--------------------|---------------------------|--|

| Amplifiers         | amplifier.ti.com       | Audio              | www.ti.com/audio          |  |

| Data Converters    | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |  |

| DSP                | dsp.ti.com             | Broadband          | www.ti.com/broadband      |  |

| Interface          | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |  |

| Logic              | logic.ti.com           | Military           | www.ti.com/military       |  |

| Power Mgmt         | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |  |

| Microcontrollers   | microcontroller.ti.com | Security           | www.ti.com/security       |  |

| Low Power Wireless | www.ti.com/lpw         | Telephony          | www.ti.com/telephony      |  |

|                    |                        | Video & Imaging    | www.ti.com/video          |  |

|                    |                        | Wireless           | www.ti.com/wireless       |  |

|                    |                        |                    |                           |  |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2006, Texas Instruments Incorporated