# Supertex inc.

## Hot Swap Controller (Negative Supply Rail)

## Features

- □ ±10V to ±90V Operation

- Built-in "normally on" turn-on clamp eliminates components

- UV/OV Lock Out & Power-on-Reset for Debouncing

- Sense resistor program ground circuit breaker

- Programmable circuit breaker holdoff

- □ Inrush control using either: i) servo or ii) feedback cap

- Feedback to Ramp pin means no Gate clamp needed

- Application solution for input voltage step (diode "ORing")

- Programmable Auto-Retry (tens of seconds if desired)

- Auto-Retry or Latched Operation

- Enable through Open Drain interface to UV or OV

- Low Power, <0.6mA PWRGD Flag Operation, <0.4mA Sleep Mode

- Small SOIC-8 Package

## Applications

-48V Central Office Switching

24V Cellular and Fixed Wireless Systems 24V PBX Systems

Line Cards

Þ

48V Powered Ethernet for VoIP

- Distributed Power Systems

- Power Supply Control

- +48V Storage Networks

- Electronic Circuit Breaker

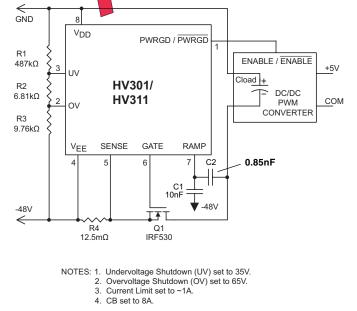

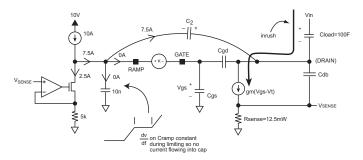

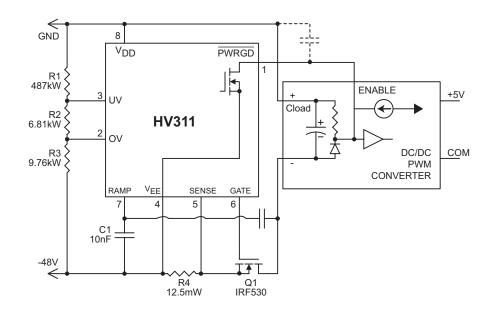

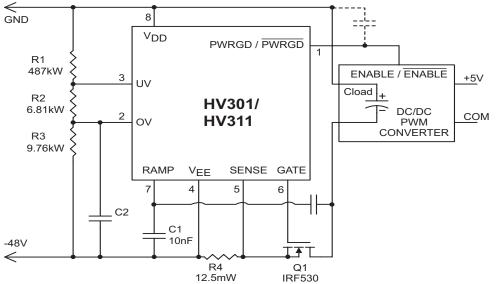

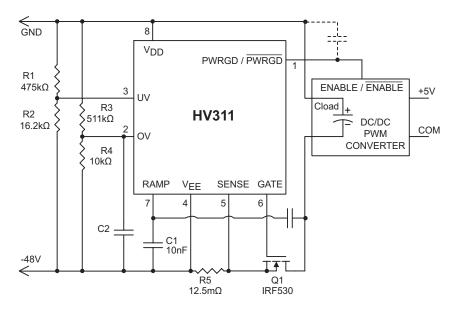

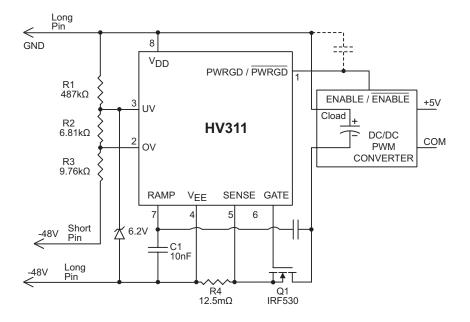

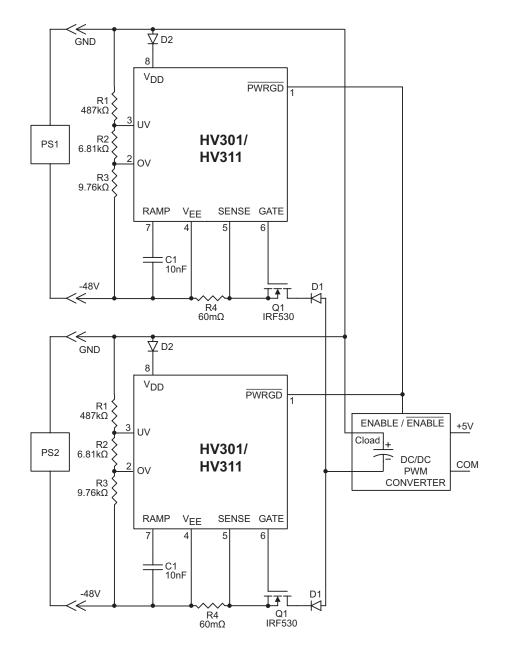

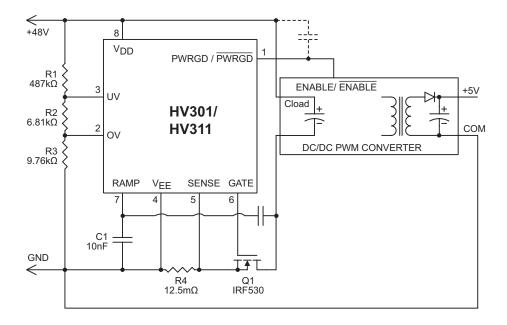

# Typical Application Circuit

## **Ordering Information**

| Active State of   | Package Options |  |  |

|-------------------|-----------------|--|--|

| Power Good Signal | 8 Pin SO        |  |  |

| HIGH              | HV301LG         |  |  |

| LOW               | HV311           |  |  |

# General Description

The Supertex HV301 and HV311 Hot Swap Centrollers provide control of power supply connection during insertion of cards or modules into live backplanes. They may be used in systems where active control is implemented in the negative lead of supplies ranging from  $\pm 10V$  to  $\pm 90V$ .

During initial power application the gate of the external pass device is clamped low to suppress contact bounce glitches by a "normally on" circuit which does not require initialization of the IC. Thereafter the UV/OV supervisors and power-on-reset work together to suppress gate turn on until mechanical bounce has ended. The HV301/311 then control the current inrush limit to a programmed level using one of two possible methods, i) servo control or ii) a grain to ramp capacitor. The above methods eliminate the need for extra hold-off or current limiting components. The devices also include an electronic circuit breaker, programmed by a sense resistor.

After the load capacitance has fully charged, the HV301/311 will transition into a low power mode, and enable the open drain PWRGD. In low power mode the HV301/311 continues to monitor the input voltage and monitor the current level. If a load fault occurs, the electronic circuit breaker will trip, the pass element will be turned off, and the PWRGD will return to an

(continued on Page 3)

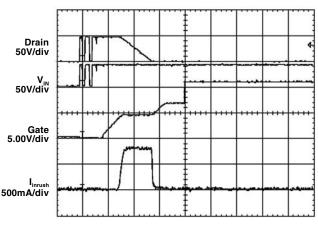

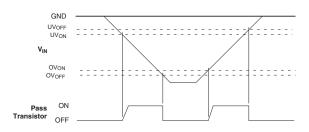

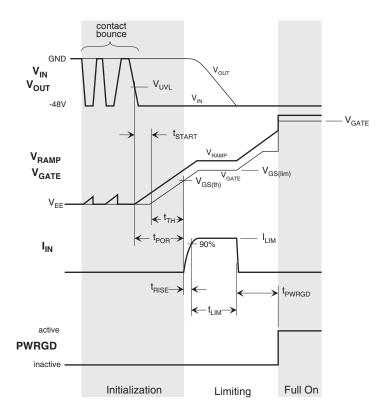

## Waveforms

5.00ms/div

A092605

## **Electrical Characteristics** (-10V - V<sub>EE</sub> - -90V, -40°C - +85°C unless otherwise noted)

| Symbol                 | Parameter                                               | Min                   | Тур      | Max                               | Units                  | Conditions                                              |

|------------------------|---------------------------------------------------------|-----------------------|----------|-----------------------------------|------------------------|---------------------------------------------------------|

| Supply                 | (Referenced to V <sub>DD</sub> pin)                     |                       |          |                                   |                        |                                                         |

| V <sub>EE</sub>        | Supply Voltage                                          | -90                   |          | -10                               | V                      |                                                         |

| I <sub>EE</sub>        | Supply Current                                          |                       | 600      | 700                               | μA                     | V <sub>EE</sub> = -48V, Mode = Limiting                 |

| I <sub>EE</sub>        | Sleep Mode Suppy Current                                |                       | 400      | 450                               | μA                     | V <sub>EE</sub> = -48V, Mode = Sleep                    |

|                        | UV Control (Referenced to V <sub>EE</sub> pin)          |                       |          | I                                 |                        |                                                         |

| V <sub>UVH</sub>       | UV High Threshold                                       |                       | 1.26     |                                   | V                      | Low to High Transition                                  |

| V <sub>UVL</sub>       | UV Low Threshold                                        |                       | 1.16     |                                   | V                      | High to Low Transition                                  |

| V <sub>UVHY</sub>      | UV Hysteresis                                           |                       | 100      |                                   | mV                     |                                                         |

| UV                     | UV Input Current                                        |                       |          | 1.0                               | nA                     | $V_{UV} = V_{EE} + 1.9V$                                |

| V <sub>OVH</sub>       | OV High Threshold                                       |                       | 1.26     |                                   | V                      | Low to High Transition                                  |

| V <sub>OVL</sub>       | OV Low Threshold                                        |                       | 1.16     |                                   | V                      | High to Low Transition                                  |

| V <sub>OVHY</sub>      | OV Hysteresis                                           |                       | 100      |                                   | mV                     |                                                         |

| lov                    | OV Input Current                                        |                       |          | 1.0                               | nA                     | $V_{OV} = V_{EE} + 0.5V$                                |

|                        | t Limit (Referenced to V <sub>EE</sub> pin)             |                       |          |                                   |                        | 1                                                       |

| V <sub>SENSE-CL</sub>  | Current Limit Threshold Voltage                         | 40                    | 50       | 60                                | mV                     | $V_{UV} = V_{EE} + 1.9V, V_{OV} = V_{EE} + 0.5V$        |

| SENSE-CB               | Circuit Breaker Threshold Voltage                       | 80                    | 100      | 120                               | mV                     | $V_{UV} = V_{EE} + 1.9V, V_{OV} = V_{EE} + 0.5V$        |

|                        | rive Output (Referenced to V <sub>EE</sub> pin)         |                       |          |                                   |                        |                                                         |

| V <sub>GATE</sub>      | Maximum Gate Drive Voltage                              | 8.5                   | 10       | 12                                | V                      | $V_{UV} = V_{FF} + 1.9V, V_{OV} = V_{FF} + 0.5V$        |

| GATEUP                 | Gate Drive Pull-Up Current                              | 500                   |          |                                   | μA                     | $V_{UV} = V_{EE} + 1.9V, V_{OV} = V_{EE} + 0.5V$        |

| GATEDOWN               | Gate Drive Pull-Down Current                            | 40                    |          |                                   | mA                     | $V_{UV} = V_{EE}, V_{OV} = V_{EE} + 0.5V$               |

| Ramp T                 | Timing Control (Test Conditions: C <sub>LOAD</sub> =100 | mF, C <sub>BAME</sub> | =10nF, V | <sub>IV</sub> =V <sub>FF</sub> +1 | .9V, V <sub>OV</sub> = | ↓<br>V <sub>FF</sub> +0.5V, External MOSFET is IRF530*) |

| RAMP                   | Ramp Pin Output Current                                 |                       | 10       |                                   | μΑ                     | V <sub>SENSE</sub> = 0V                                 |

| t <sub>POR</sub>       | Time from UV to Gate Turn On                            | 2.0                   |          |                                   | ms                     | (See Note 1)                                            |

| RISE                   | Time from Gate Turn On to V <sub>SENSE</sub> Limit      | 400                   |          |                                   | μs                     |                                                         |

| t <sub>limit</sub>     | Duration of Current Limit Mode                          |                       | 5.0      |                                   | ms                     |                                                         |

| PWRGD                  | Time from Current Limit to PWRGD                        |                       | 5.0      |                                   | ms                     |                                                         |

| V <sub>RAMP</sub>      | Voltage on Ramp Pin in Current Limit Mode               |                       | 3.6      |                                   | V                      | (See Note 2)                                            |

|                        | Start Up Time Limit                                     | 80                    | 100      | 120                               | ms                     |                                                         |

|                        | Circuit Breaker Delay Time                              | 2.0                   |          | 5.0                               | μs                     | May be exteneded by external RC circuit                 |

| t <sub>AUTO</sub>      | Automatic Restart Delay TIme                            | 12                    |          |                                   | s                      |                                                         |

|                        | Good Output (Referenced to V <sub>EE</sub> pin)         | 1                     |          | 1                                 | 1                      | 1                                                       |

| V <sub>PWRGD(hi)</sub> | Applied voltage to PWRGD                                | 90                    |          |                                   | V                      | PWRGD=Inactive                                          |

| V <sub>PWRGD(lo)</sub> | PWRGD Low Voltage                                       |                       | 0.5      | 0.8                               | V                      | I <sub>PWRGD</sub> = 1mA, PWRGD=Active                  |

|                        | ic Characteristics                                      | -                     |          | -                                 |                        |                                                         |

|                        |                                                         |                       |          |                                   |                        |                                                         |

|                        | OV Comparator Transition                                |                       |          | 500                               | ns                     |                                                         |

Note 1: This timing depends on the threshold voltage of the external N-Channel MOSFET. The higher its threshold is, the longer this timing.

Note 2: This voltage depends on the characteristics of the external N-Channel MOSFET.  $V_{th} = 3V$  for an IRF530.

\* IRF530 is a registered trademark of International Rectifier.

## General Description, cont'd.

inactive state. Thereafter a programmable auto-retry timer will hold the device off to allow the pass element to cool before resetting and restarting. The auto-retry can be disabled using a single resistor if desired.

The HV301/311 includes a current mode servo-circuit which can be used as a return to limit during input voltage steps such as would be seen in a diode "ORed" situation when power switches back to regulated supply from battery operation. The HV301/311 allows independent programming of the trigger level of this phenomenon so that it may be set at a different level to the current limit level if desired. Under all circumstances the maximum servo period is limited to 100ms to protect the pass element.

## **PWRGD Logic**

| Model  | Condition            | PWRGD |                 |  |

|--------|----------------------|-------|-----------------|--|

| HV301  | INACTIVE (Not Ready) | 0     | VEE             |  |

| 110301 | ACTIVE (Ready)       | 1     | HI Z            |  |

| HV311  | INACTIVE (Not Ready) | 1     | HI Z            |  |

| 110311 | ACTIVE (Ready)       | 0     | V <sub>EE</sub> |  |

## **Absolute Maximum Ratings**

| $V_{\text{EE}}$ reference to $V_{\text{DD}}$ pin                                            | +0.3V to -100V  |

|---------------------------------------------------------------------------------------------|-----------------|

| $V_{\mbox{\tiny PWRGD}}$ referenced to $V_{\mbox{\tiny EE}}$ Voltage                        | -0.3V to +100V  |

| $V_{\mbox{\tiny UV}}$ and $V_{\mbox{\tiny OV}}$ referenced to $V_{\mbox{\tiny EE}}$ Voltage | -0.3V to +12V   |

| Operating Ambient Temperature                                                               | -40°C to +85°C  |

| Operating Junction Temperature                                                              | -40°C to +125°C |

| Storage Temperature Range                                                                   | -65°C to +150°C |

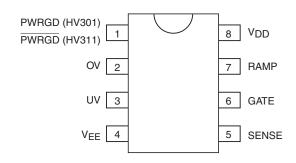

## Pinout

## **Pin Description**

**PWRGD** – The Power Good Output Pin is held inactive on initial power application and will go active when the external MOSFET is fully turned on. This pin may be used as an enable control when connected directly to a PWM power module.

**OV** – This Over Voltage sense pin, when raised above its high threshold will immediately cause the GATE pin to be pulled low. The GATE pin will remain low until the voltage on this pin falls below the low threshold limit, initiating a new start-up cycle.

**UV** – This Under Voltage sense pin, when below its low threshold limit will immediately cause the GATE pin to be pulled low. The GATE pin will remain low until the voltage on this pin rises above the high threshold limit, initiating a new start-up cycle.

$\mathbf{V}_{\text{EE}}$  – This pin is the negative terminal of the power supply input to the circuit.

$\mathbf{V}_{\text{DD}}$  – This pin is the positive terminal of the power supply input to the circuit.

**RAMP** – This pin provides a current output so that a timing ramp voltage is generated when a capacitor is connected.

**GATE** – This is the Gate Driver Output for the external N-Channel MOSFET.

**SENSE** – The current sense resistor connected from this pin to  $V_{\text{FE}}$  Pin programs the circuit breaker trip limit.

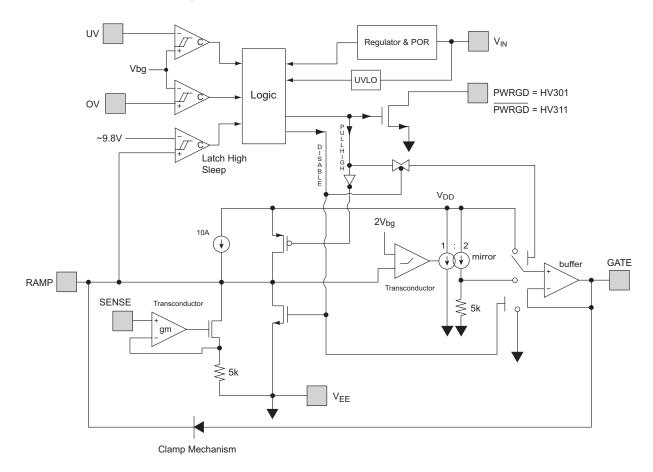

## **Functional Block Diagram**

## **Functional Description**

#### **Insertion into Hot Backplanes**

Telecom, data networks and some computer applications require the ability to insert and remove circuit cards from systems without powering down the entire system. All circuit cards have some filter capacitance on the power rails, which is especially true in circuit cards or network terminal equipment utilizing distributed power systems. The insertion can result in high inrush currents that can cause damage to connector and circuit cards and may result in unacceptable disturbances on the system backplane power rails.

The HV301 and HV311 are designed to facilitate the insertion of these circuit cards or connection of terminal equipment by eliminating these inrush currents and powering up these circuits in a controlled manner after full connector insertion has been achieved. The HV301 or HV311 is intended to provide this function on supply rails in the range of  $\pm 10$  to  $\pm 90$  Volts.

#### **Description of Operation**

During initial power application, a unique proprietary circuit holds off the external MOSFET, preventing an input glitch while an internal regulator establishes an internal operating voltage of approximately 10V. Until the proper internal voltage is achieved all circuits are held reset, the PWRGD output is inactive and the gate to source voltage of the external MOSFET is clamped low. Once the internal under voltage lock out (UVLO) has been satisfied, the circuit checks the input supply under voltage (UV) and over voltage (OV) sense circuits to ensure that the input voltage is within programmed limits. These limits are determined by the selected values of resistors R1, R2 and R3, which form a voltage divider.

Assuming the above conditions are satisfied and while continuing to hold the PWRGD output inactive and the external MOSFET GATE voltage low, the current source feeding the RAMP pin is turned on. The external capacitor connected to it begins to charge, thus starting an initial time delay determined by the value of the capacitor. During this time if the OV or UV limits are exceeded, an immediate reset occurs and the capacitor connected to the RAMP pin is discharged.

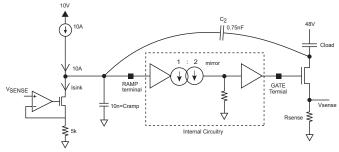

When the voltage on the RAMP pin reaches an internally set threshold voltage, the gate drive circuit begins to turn on the external MOSFET. In servo mode, once the gate threshold is reached, the resulting output current generates a voltage drop on the sense resistor connected between the SENSE and  $V_{\text{EE}}$  pins, causing a decrease in the available current charging the capacitor on the RAMP pin. This continuous feedback mechanism allows the output current to rise inverse exponentially over a period of a few hundred microseconds to the sense resistor programmed current limit set point.

When the voltage drop on the sense resistor reaches 50mV the

## Functional Description, cont'd.

RAMP pin current is reduced to zero and the voltage on the RAMP pin will be fixed, indicating that the circuit is in current limit mode. Depending on the value of the load capacitor and the programmed current limit, charging may continue for some time, but may not exceed a nominal 100ms preset time limit. Once the load capacitor has been charged, the output current will drop, reducing the voltage on the SENSE pin, which in turn will increase the RAMP pin current, thus causing the voltage on the capacitor connected to the RAMP pin to continue rising, thereby providing yet another programmed delay. If due to output overload conditions during startup, PWRGD does not achieve an active state within 100ms or the Circuit Breaker is tripped, the circuit is reset, pulling down the GATE to V<sub>EE</sub>, discharging the capacitor connected to the RAMP pin, changing PWRGD to an inactive state. A timeout or circuit breaker fault will initiate an Auto-Retry if enabled.

On the other hand, in feedback capacitor mode, a current source of  $10\mu A$  from the RAMP pin limits the dv/dt of the feedback

capacitor which, in turn, programs Inrush according to Inrush=10  $\mu A\text{-}C_{\text{load}}/C_2.$

When the ramp voltage is within 1.2V of the regulated internal supply voltage, the controller will force the GATE terminal to a nominal 10V, the PWRGD pin will change to an active state, the Circuit Breaker is enabled and the circuit will transition to a low power sleep mode.

When the voltage on the SENSE pin rises to 100mV, indicating an over current condition, the circuit breaker will trip in less than  $5\mu$ s. This time may be extended by the addition of external components.

At any time during the start up cycle or thereafter, crossing the UV and OV limits (including hysteresis) will cause an immediate reset of all internal circuitry. When the input supply voltage returns to a value within the programmed UV and OV limits a new start up sequence will be initiated.

## **Design Information**

#### Setting Under Voltage and Over Voltage Shut Down

The UV and OV pins are connected to comparators with nominal 1.21V thresholds and 100mV of hysteresis  $(1.21V \pm 50mV)$ . They are used to detect under voltage and over voltage conditions at the input to the circuit. Whenever the OV pin rises above its high threshold (1.26V) or the UV pin falls below its low threshold (1.16V) the GATE voltage is immediately pulled low, the PWRGD pin changes to its inactive state and the external capacitor connected to the RAMP pin is discharged.

Calculations can be based on either the desired input voltage operating limits or the input voltage shutdown limits. In the following equations the shutdown limits are assumed.

The under voltage and over voltage shut down thresholds can be programmed by means of the three resistor divider formed by R1, R2 and R3. Since the input currents on the UV and OV pins are negligible the resistor values may be calculated as follows:

$$UV_{OFF} = V_{UVL} = 1.16 = \left| V_{EEUV(off)} \right| \times \frac{R2 + R3}{R1 + R2 + R3}$$

$$OV_{OFF} = V_{OVH} = 1.26 = \left| V_{EEOV(off)} \right| \times \frac{R3}{R1 + R2 + R3}$$

Where  $|V_{EEUV(off)}|$  and  $|V_{EEOV(off)}|$  relative to  $V_{EE}$  are Under & Over Voltage Shut Down Threshold points.

If we select a divider current of 100 $\mu$ A at a nominal operating input voltage of 50 Volts then

$$R1 + R2 + R3 = \frac{50V}{100\mu A} = 500k\Omega$$

From the second equation for an OV shut down threshold of 65V the value of R3 may be calculated.

$$OV_{OFF} = 1.26 = \frac{65 \times R3}{500 \text{k}\Omega}$$

$$R3 = \frac{1.26 \times 500 \mathrm{k}\Omega}{65} = 9.69 \mathrm{k}\Omega$$

The closest 1% value is  $9.76k\Omega$ .

From the first equation for a UV shut down threshold of 35V the value of R2 can be calculated.

$$UV_{OFF} = 1.16 = \frac{35 \times (R2 + R3)}{500 \mathrm{k}\Omega}$$

$$R2 = \frac{1.16 \times 500 \mathrm{k}\Omega}{35} - 9.76 \mathrm{k}\Omega = 6.81 \mathrm{k}\Omega$$

The closest 1% value is  $6.81k\Omega$ .

Then

$R1 = 500 \mathrm{k}\Omega - R2 - R3 = 483 \mathrm{k}\Omega$

The closest 1% value is  $487k\Omega$ .

## Design Information, cont'd.

#### Undervoltage/Overvoltage Operation

From the calculated resistor values the OV and UV start up threshold voltages can be calculated as follows:

$$UV_{ON} = V_{UVH} = 1.26 = |V_{EEUV(on)}| \times \frac{R2 + R3}{R1 + R2 + R3}$$

$$OV_{ON} = V_{OVL} = 1.16 = |V_{EEOV(on)}| \times \frac{R3}{R1 + R2 + R3}$$

Where  $|V_{EEUV(on)}|$  and  $|V_{EEOV(on)}|$  are Under & Over Voltage Start Up Threshold points relative to  $V_{EE}$ .

Then

$$|V_{EEUV(on)}| = 1.26 \times \frac{R1 + R2 + R3}{R2 + R3}$$

$$|V_{EEUV(on)}| = 1.26 \times \frac{487k\Omega + 6.81k\Omega + 9.76k\Omega}{6.81k\Omega + 9.76k\Omega} = 38.29V$$

And

$$|V_{EEOV(on)}| = 1.16 \times \frac{R1 + R2 + R3}{R3}$$

$|V_{EEOV(on)}| = 1.16 \times \frac{487 \text{k}\Omega + 6.81 \text{k}\Omega + 9.76 \text{k}\Omega}{9.76 \text{k}\Omega} = 59.85 \text{V}$

Therefore, the circuit will start when the input supply voltage is in the range of 38.29V to 59.85V.

### Programming Inrush and $I_{CB}$

#### Method 1: Inrush independent of I<sub>CB</sub>

1. Choose circuit breaker trip point eg. 8A as follows

Rsense =

$$\frac{100mV}{I_{CR}} = \frac{100mV}{8} = 12.5m\Omega$$

2. Choose inrush level, for example Inrush=1A

3. Calculate Isink =

$$\frac{\text{Inrush} * \text{Rsense}}{5k\Omega} = \frac{1A \times 12.5m\Omega}{5k\Omega} = 2.5\mu\text{A}$$

- 4. Calculate  $C_2$  discharge limit =  $10\mu$ A - Isink = 7.5 $\mu$ A (typical) = i $C_2$

- 4a. Adjust for Auto-retry disable, if used  $\rightarrow$

$$\approx \frac{Vt_{max}}{R_{disable}} \text{ e.g. } \frac{4V}{2.5M\Omega} = 1.6\mu\text{A}$$

$$\Rightarrow \text{ e.g. iC}_2 = 10\mu\text{A} - \text{Isink} - 1.6\mu\text{A}$$

In this example we assume Auto-retry is enabled so ignore 1.6 $\mu$ A,  $\therefore$  iC<sub>2</sub> = 10 $\mu$ A-Isink = 7.5 $\mu$ A

5. Note:  $i = C \frac{dv}{dt}$   $iC_2 = C_2 \times \frac{dv}{dt}$  Inrush =  $C_{load} \times \frac{dv}{dt}$

Note V<sub>IN</sub> is fixed and V<sub>RAMP</sub> is constant during limiting  $\Rightarrow \frac{dv}{dt} \operatorname{across} C_{\text{load}} = \frac{dv}{dt} \operatorname{across} C_2$  (as they share a common node and their other terminals are fixed during inrush)

$$\frac{iC_2}{C_2} = \frac{Inrush}{C_{load}} \implies \text{Inrush} = \frac{iC_2 \times C_{load}}{C_2}$$

by conservation of charge on RAMP Node iC<sub>2</sub> =  $7.5\mu$ A

Inrush =

$$\frac{7.5\mu A \times C_{load}}{C_2}$$

$\Rightarrow$  C<sub>2</sub> =  $\frac{7.5\mu A \times C_{load}}{Inrush}$

7.5 $\mu A \times 100nF$  = 5.5 C = 5.5

$=\frac{7.5\mu A \times 100 nT}{1A} = 750 \text{pF} = 0.75 \text{nF}$

Note that RAMP is protected by AC divider and Gate is clamped internally.

## Design Information, cont'd.

### Programming Inrush and I<sub>CB</sub>, continued:

#### Method 2: Inrush = $1/2 I_{CB}$

- 1. Choose I<sub>CB</sub> =  $\frac{100mV}{R_{SENSE}}$ , e.g. 2A  $\Rightarrow$  R<sub>SENSE</sub> = 50m $\Omega$

- 2. Inrush =  $\frac{50mv}{R_{SENSE}}$ , e.g.  $\frac{50mV}{50m\Omega}$  = 1A

- 3. Add compensation components from gate to drain if necessary to reduce peaking.

- i) start with 2nF from gate to source

- ii) increase to 10nF if needed

- iii) add 1k Series resistor from gate to capacitor if needed

### Timing

The timing functions are defined by the following equations:

$$t_{START} = 2.4 \frac{C_{RAMP}}{I_{RAMP}}$$

$$t_{TII} = V_{CS(4)} \frac{C_{RAMP}}{I_{RAMP}}$$

$$V_{TH} = V_{GS(th)} I_{RAMP}$$

$$t_{POR} = t_{START} + t_{TH}$$

$$t_{RISE} \approx \frac{C_{RAMP}}{g_{fs} \left(\frac{I_{RAMP}}{0.9I_{LIMIT}} - \frac{R_{SENSE}}{R_{FB}}\right)}$$

$$t_{LIMIT} \approx V_{IN} \frac{C_{LOAD}}{I_{LIMIT}}$$

$$t_{PWRGD} = \left(V_{INT} - V_{GS(\mathsf{LIMIT})} - 1.2\right) \frac{C_{RAMP}}{I_{RAMP}}$$

## Design Information, cont'd.

These equations assume that the load is purely capacitive and the following definitions apply.

$C_{\text{BAMP}}$  is the external capacitor connected to the RAMP pin.

$I_{RAMP}$  is the output current from the RAMP pin, nominally 10µA, when the voltage drop on  $R_{SENSE}$  resistor is zero.

$V_{\rm INT}$  is the internally regulated supply voltage and can range from 8.5V to 12V.

$V_{GS(th)}$  is the gate threshold voltage of the external pass transistor and may be obtained from its datasheet.

$V_{GS(\text{limit})}$  is the external pass transistor gate-source voltage required to obtain the limit current. It is dependent on the pass transistor's characteristics and may be obtained from the transfer characteristics on the transistor datasheet.

$g_{is}$  is the transconductance of the external pass transistor and may be obtained from its datasheet.

$R_{_{FB}}$  is the internal feedback resistor and is nominally 5k $\Omega$ .

$\textit{I}_{\textit{LIMIT}}$  is the load current when the voltage drop on the  $\textit{R}_{\text{SENSE}}$  resistor is 50mV.

These equations may be used to calculate the minimum value of  $C_{\rm RAMP}$  for the most critical system performance characteristics.

For maximum contact bounce duration protection choose a value for  $t_{POR}$  and use the following equation:

$$C_{RAMP} = \frac{t_{POR} \times I_{RAMP}}{2.4 + V_{GS(th)}}$$

If control of PWRGD active delay is the critical system parameter, then choose a value for  $t_{PWRGD}$  and use the following equation:

$$C_{RAMP} = \frac{t_{PWRGD} \times I_{RAMP}}{V_{INT} - V_{GS(\text{limit})} - 1.2}$$

#### Start up Overload Protection

Start up must be achieved within a nominal 100ms as indicated by the PWRGD pin transition to the active state or the circuit will reset and an automatic restart will initiate after 12s delay. If there is an output overload or short circuit during start up, the circuit will be in a current mode for the 100ms time limit.

#### **Circuit Breaker**

The circuit breaker will trip in less than 5µs when the voltage on the SENSE pin reaches a nominal 100mV (2.0 x I<sub>LIMIT</sub>). A resistor in series with the SENSE pin and a capacitor connected between the SENSE and V<sub>EE</sub> pins may be added to delay the rate of voltage rise on the SENSE pin, thus permitting a current overshoot and delaying Circuit Breaker activation.

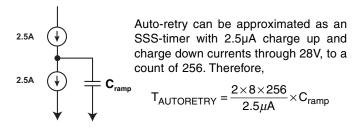

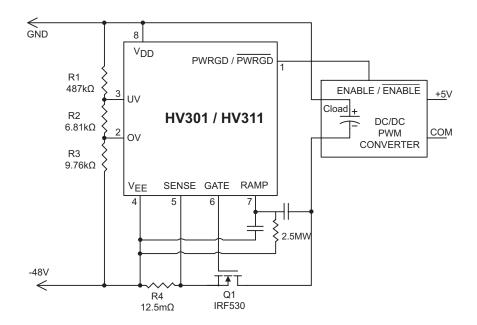

#### **Automatic Restart**

The Automatic Restart delay time is directly proportional to the capacitance at the RAMP pin. Automatic Restart sequence is activated whenever the 100ms timeout is reached during start up or the Circuit Breaker is tripped in low power sleep operating mode.

Due to the  $2.5\mu$ A max charge current a resistor which draws more than  $2.5\mu$ A below 8V will disable the autoretry. Try to keep this resistor as big as possible, e.g. 2.5mý, for most MOSFETs with max V<sub>t</sub> of 4V this will vary the 10 $\mu$ A current source by only 4/2.5mý=1.6 $\mu$ A.

## **Application Information**

#### **Supported External Pass Devices**

The HV301 and HV311 are designed to support N-Channel MOSFETs and IGBTs.

#### **Selection of External Pass Devices**

Since the current limit is likely to be set just slightly higher than maximum continuous load current in a typical system, the continuous current rating of the device will have to be at least equal to the current limit value.

The  $R_{DS(ON)}$  of the device is likely to be selected based on allowable voltage drop after the hot swap action has been completed. Thus the continuous power dissipation rating of the device can be determined from the following equation:

$$P_{CONT} = R_{DS(ON)} \times I_{LIMIT}^2$$

The peak power rating may be calculated from the following equation:

$$P_{PEAK} = V_{IN} \times I_{LIMIT}$$

Given these values an external pass transistor may be selected from the manufacturers data sheet.

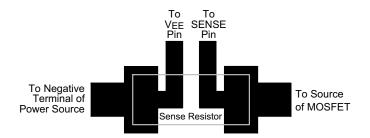

#### Selection of Current Sense Resistor

The power rating of the sense resistor must be greater than  $I_{load}^2 \times R$ , where  $I_{load}$  is the normal maximum operating load.

#### Kelvin Connection to Sense Resistor

Physical layout of the printed circuit board is critical for correct current sensing. Ideally trace routing between the current sense resistor and the V<sub>EE</sub> and SENSE pins should be direct and as short as possible with zero current in the sense traces. The use of Kelvin connection from SENSE pin and V<sub>EE</sub> pin to the respective ends of the current sense resistor is recommended.

#### Paralleling External Pass Transistors

Due to variations in threshold voltages and gain characteristics between samples of transistors reliable 50% current sharing is not achievable. Some measure of paralleling may be accomplished by adding resistors in series with the source of each device; however, it will cause increased voltage drop and power dissipation.

#### Paralleling of external Pass devices is not recommended!

If a sufficiently high current rated external pass transistor cannot be found then increased current capability may be achieved by connecting independent hot swap circuits in parallel, since they act as current sources during the load capacitor charging time when the circuits are in current limit. For this application the HV301 with active high PWRGD is recommended where the PWRGD pins of multiple hot swap circuits can be connected in a wired OR configuration.

#### **PWRGD** Output

It is critical to have a detailed understanding of the ENABLE input circuitry of the load (DC/DC PWM Converter) in order to make the correct choice between the HV301 and HV311.

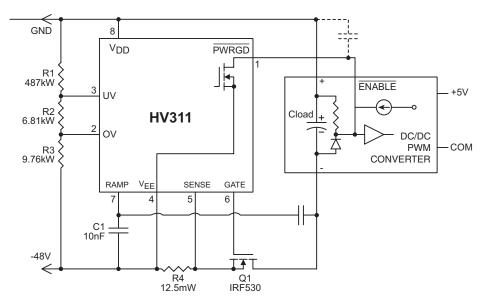

Many DC/DC PWM Converters reference their ENABLE inputs to the negative input terminal. If the ENABLE input is active LOW

then the HV311 can be directly connected as shown below (**Application Circuit 1**) since the open drain PWRGD output is in a High-Z state until the external MOSFET is fully turned on and the potential on the negative input of the converter is essentially the same as the  $V_{\text{EE}}$  pin of the HV311.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{IN}$  is close to OVLO.

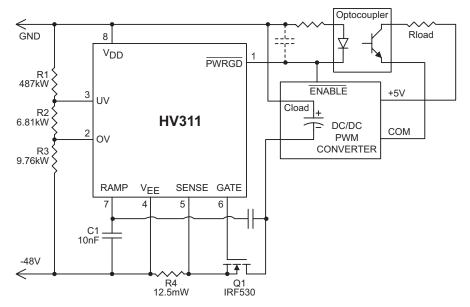

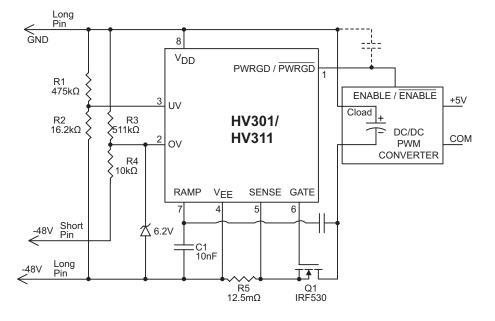

However, if the DC/DC PWM Converter with the ENABLE input circuit configuration was active HIGH, then the apparent choice of the HV301 would result in the creation of a current path through the protective diode clamp of the ENABLE input and the PWRGD output MOSFET of the HV301. For this situation the HV311 should be used as shown below in **Application Circuit 2**.

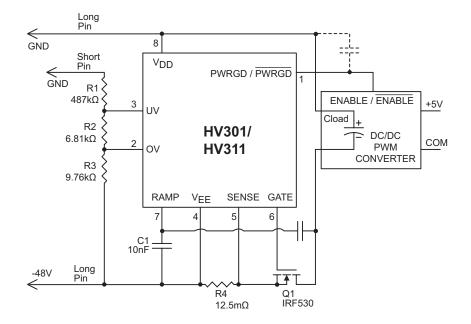

### **Application Circuit 1**

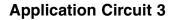

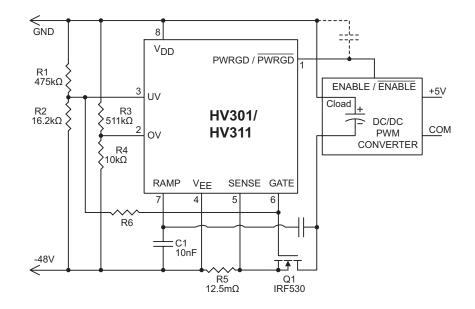

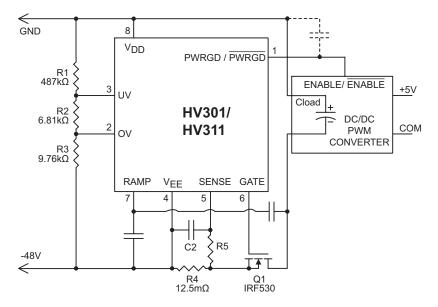

In some applications the PWRGD signal is used to activate load circuitry on the isolated output side of the DC/DC PWM Converter. In this situation an optocoupler is needed to provide the required isolation as shown below in **Application Circuit 3**.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{IN}$  is close to OVLO.

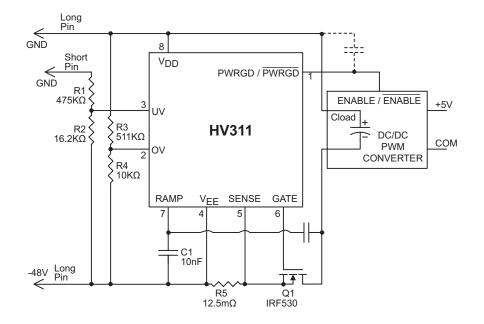

### **Application Circuit 2**

A092605

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when V\_{\rm IN} is close to OVLO.

When the details of the load ENABLE circuitry is not known, using an optocoupler always provides a safe solution (**Application Circuit 4**).

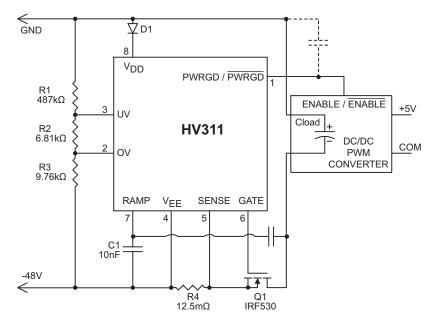

#### Filtering Voltage Spikes on Input Supply

In some systems over voltage spikes of very short duration may exist. For these systems a small capacitor may be added from the OV pin to the  $V_{\text{EE}}$  pin to filter the voltage spikes (**Application Circuit 5**).

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when V\_{\rm IN} is close to OVLO.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{\mbox{\tiny IN}}$  is close to OVLO.

### **Application Circuit 5**

Unfortunately this will also cause some delay in responding to UV conditions. If this UV delay is not acceptable, then separate resistor dividers can be provided for OV and UV with a capacitor connected from OV pin to the  $V_{EE}$  pin (**Application Circuit 6**).

#### **Using Short Connector Pin**

In some systems short connector pins are used to guarantee that the power pins are fully mated before the hot swap control circuit is enabled. For these systems the positive  $(V_{DD})$  end of the R1, R2, and R3 resistor divider should be connected to the short pin (**Application Circuit 7**).

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{\rm IN}$  is close to OVLO.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when V\_{\rm IN} is close to OVLO.

### **Application Circuit 6**

If separate resistor dividers are used for OV and UV, then only the positive  $(V_{DD})$  end of the UV resistor divider should be connected to the short pin (**Application Circuit 8**).

mated before the hot swap control circuit is enabled and a single resistor divider string (R1, R2 and R3) is used, then a 6.2V to 10V zener diode must be connected from the UV pin to the  $V_{\text{EE}}$  pin, as seen below in **Application Circuit 9**.

If a system requires the use of a short connector pin on the negative supply lead to guarantee that the power pins are fully

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{IN}$  is close to OVLO.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when V\_{\rm IN} is close to OVLO.

### **Application Circuit 9**

If a system requires the use of a short connector pin on the negative supply lead to guarantee that the power pins are fully mated before the hot swap control circuit is enabled and uses separate resistor dividers for UV and OV, then a 6.2V to 10V zener diode must be connected from the OV pin to the  $V_{EE}$  pin and only the OV divider should be connected to the short pin (**Application Circuit 10**).

#### **Increasing Under Voltage Hysteresis**

If the internally fixed under voltage hysteresis is insufficient for a particular system application, then it may be increased by using separate resistor dividers for OV and UV and providing a resistor feedback path from the GATE pin to the UV pin (**Application Circuit 11**).

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{\text{IN}}$  is close to OVLO.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when V\_{\rm IN} is close to OVLO.

### **Application Circuit 11**

#### **Reverse Polarity Protection**

The UV and OV pins are protected against reverse polarity input supplies by internal clamping diodes and the fault currents are sufficiently limited by the impedance of the external resistor divider, however, a low current diode with a 100V breakdown rating must be inserted in series with the  $V_{DD}$  pin.

This method (shown in **Application Circuit 12**) will protect the hot swap control circuit however, due to the intrinsic diode in the external MOSFET, the load will not be protected from reverse polarity voltages.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{IN}$  is close to OVLO.

#### **Redundant Supplies**

Many systems use redundant primary power supplies or battery backup. When redundant AC powered sources are used they are generally diode OR'ed to the load on the hot terminal.

For these systems, the use of independent hot swap controllers is recommended with the diode OR'ing provided after the hot

swap controllers. The HV311 is ideally suited for such applications since two or more active low PWRGD signals can be connected to a single active low ENABLE pin, thus enabling the load as long as at least one primary power source is available. By adding low current 100V diodes in series with the  $V_{DD}$  pins, full reverse polarity protection on either power source is also provided (**Application Circuit 13**).

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when V<sub>IN</sub> is close to OVLO.

#### **Use with Negative Ground**

The HV301 and HV311 may be used with many positive ground systems where DC/DC PWM Converters have isolated outputs and their inputs need not be ground referenced (**Application Circuit 14**).

### HV301/HV311

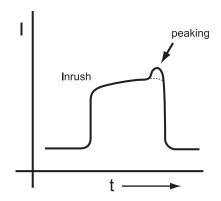

#### Current Limit Stability (Method 2 (Servo) Only)

The closed loop current mode control system used in the HV301/ HV311 is very stable, especially when driving MOSFETs with high gate capacitances ( $C_{\rm ISS}$ ). However, a peaking in I<sub>LIMIT</sub> near the end of the current limit may be noted with some MOSFETs. The current control loop can be frequency compensated to eliminate this peaking by adding a series connected capacitor and resistor between the gate and source of the external MOSFET. The recommended starting values for C and R are 10nF and 1K. These compensation values should be verified by board level testing, which may yield satisfactory results with reduced component values.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when V<sub>IN</sub> is close to OVLO.

#### **Extending Circuit Breaker Delay**

Connecting a resistor in series with the SENSE pin and a capacitor between the SENSE and  $V_{EE}$  pins as shown in the following diagram may be used to extend the Circuit Breaker delay time beyond the 5µs internally set delay time (**Application Circuit 15**).

The time delay achievable by this method is limited since this

delay circuit will also effect the current control feedback loop and will result in a current overshoot during the external pass device turn on transition to current limit. If the time delay required for the Circuit Breaker causes excessive current overshoot during the turn on transition then the following circuit may be used, where the RC filter is switched on after the completion of the current limit control function of the hot swap controller.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{\rm IN}$  is close to OVLO. Latched Operation

For those applications that need to disable the automatic retry capability, the following circuit disables the auto retry feature.

Note: capacitor may be needed to slow PWRGD dv/dt if gate oscillations around are observed when  $V_{IN}$  is close to OVLO.

**Application Circuit 15**

Application Circuit 17 A092605

# HV301/HV311

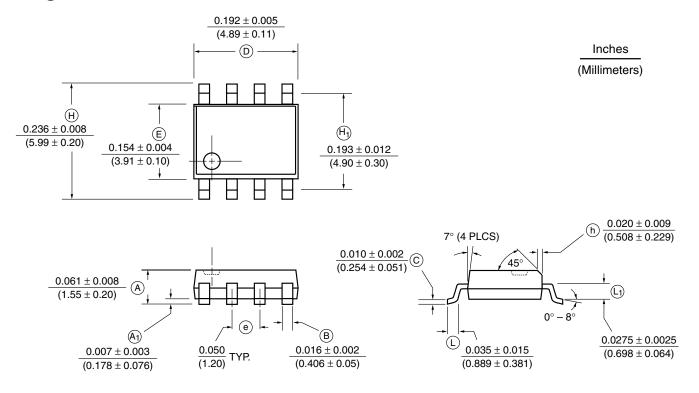

## **Package Dimensions**

Circled letters (e.g. (B) denote JEDEC reference dimensons.

# **Technical Update / Alert**

### This alert applies to the HV301, HV302, HV311, and HV312 Hotswap Controllers

The internal circuit breaker may trip unintentionally in situations when the voltage at the  $V_{DD}$  pin rises slowly as power is applied.

This unintended tripping of the circuit breaker causes the power-on sequence to be delayed by an additional Automatic Restart Delay. The extra delay can be observed by viewing the voltage waveform at the RAMP pin.

Subsequent to this delay, this device will perform a regular start-up, thereby providing power to the load.

The inadvertant tripping of the circuit breaker does not occur when the input voltage slew rate is greater than 400V per ms. In a typical hotswap application, the rise of the input voltage occurs in a couple of microseconds, and the slew rate is well in excess of of the value necessary to cause tripping of the circuit breaker.

If technical assistance is required, please contact our applications department by e-mail at <u>apps@supertex.com</u>, or by telephone at 408-222-4895.

**Supertex inc.** does not recommend the use of its products in life support applications and will not knowingly sell its products for use in such applications unless it receives an adequate "products liability indemnification insurance agreement". **Supertex** does not assume responsibility for use of devices described and limits its liability to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions or inaccuracies. Circuitry and specifications are subject to change without notice. For the latest product specifications, refer to the **Supertex** website: http://www.supertex.com. For complete liability information on all **Supertex** products, refer to the most current databook.

©2005 Supertex inc. All rights reserved. Unauthorized use or reproduction is prohibited.

**Supertex Inc.** 1235 Bordeaux Drive, Sunnyvale, CA 94089 TEL: (408) 222-8888 / FAX: (408) 222-4895 *www.supertex.com*