|                                                                                                 |                                                        |                                    |                  |                                                            |                                                         |                                   |                    | F        | REVISI           | IONS                |                    |                              |                            |                              |                   |                               |                                          |                           |           |     |

|-------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------------------|------------------|------------------------------------------------------------|---------------------------------------------------------|-----------------------------------|--------------------|----------|------------------|---------------------|--------------------|------------------------------|----------------------------|------------------------------|-------------------|-------------------------------|------------------------------------------|---------------------------|-----------|-----|

| LTR                                                                                             |                                                        |                                    |                  |                                                            | ĺ                                                       | DESCR                             | RIPTIO             | N        |                  |                     |                    |                              |                            | DATE (\                      | /R-MO-D           | A)                            |                                          | APPR                      | ROVED     |     |

| Α                                                                                               | Add vo                                                 | endor (<br>e boile                 | CAGE<br>rplate t | F8859.<br>to MIL-f                                         | Add c                                                   | ase ou<br>3535 re                 | tline X.<br>quirem | Add ta   | able III,<br>JAK | , delta l           | mits.              |                              | 01-12-18                   |                              |                   |                               | Thomas M. Hess                           |                           |           |     |

| В                                                                                               | wavef                                                  | orms ir                            | figure           | 4. Up                                                      | date th                                                 | 1.5, race boiler changes          | plate to           | o includ | de radia         | ke char<br>ation ha | nges to<br>ordness | ;                            |                            | 05-0                         | 5-04-21           |                               | Т                                        | homas                     | M. He     | SS  |

|                                                                                                 |                                                        |                                    |                  |                                                            |                                                         |                                   |                    |          |                  |                     |                    |                              |                            |                              |                   |                               |                                          |                           |           |     |

|                                                                                                 |                                                        |                                    |                  |                                                            |                                                         |                                   |                    |          |                  |                     |                    |                              |                            |                              |                   |                               |                                          |                           |           |     |

| DEV                                                                                             |                                                        |                                    |                  |                                                            |                                                         |                                   |                    |          |                  | 1                   |                    |                              |                            |                              |                   |                               |                                          |                           |           |     |

| REV                                                                                             |                                                        |                                    |                  |                                                            |                                                         |                                   |                    |          |                  |                     |                    |                              |                            |                              |                   |                               |                                          |                           |           |     |

| SHEET                                                                                           | B                                                      | R                                  |                  |                                                            |                                                         |                                   |                    |          |                  |                     |                    |                              |                            |                              |                   |                               |                                          |                           |           |     |

| SHEET                                                                                           | B 15                                                   | B 16                               |                  |                                                            |                                                         |                                   |                    |          |                  |                     |                    |                              |                            |                              |                   |                               |                                          |                           |           |     |

| SHEET<br>REV<br>SHEET                                                                           | B 15                                                   | B<br>16                            |                  | REV                                                        |                                                         |                                   | В                  | В        | В                | В                   | В                  | В                            | В                          | В                            | В                 | A                             | В                                        | В                         | В         |     |

| SHEET REV SHEET REV STATUS                                                                      |                                                        |                                    |                  | REV                                                        |                                                         |                                   | B 1                | B 2      | B 3              | B 4                 | B 5                | B 6                          | B 7                        | B 8                          | B 9               | A 10                          | B 11                                     | B 12                      | B 13      | E 1 |

|                                                                                                 |                                                        |                                    |                  | SHE                                                        | ET<br>PARED                                             | BY<br>Kellehe                     | 1                  |          |                  | -                   | 5                  | 6<br>EFEN                    | 7<br>SE SI                 | 8<br>UPPL                    | 9<br><b>Y CE</b>  | 10                            | 11 COL                                   | 12<br>.UMB                | 13        |     |

| SHEET REV SHEET REV STATUS OF SHEETS PMIC N/A                                                   | 15                                                     | 16<br>RD                           |                  | SHEE<br>PREF<br>Mar                                        | ET<br>PARED<br>cia B. I                                 | Kellehe<br>3Y                     | 1                  |          |                  | -                   | 5                  | 6<br>EFEN                    | 7<br>SE SI                 | 8<br>UPPL                    | 9<br>Y CE<br>OHIO | 10<br>NTER<br>D 432           | 11<br>COL<br>218-39                      | 12<br>.UMB                | 13        |     |

| SHEET REV SHEET REV STATUS OF SHEETS PMIC N/A STAI                                              | 15                                                     | 16                                 |                  | SHEE<br>PREF<br>Mar<br>CHEC<br>Ray                         | ET<br>PARED<br>cia B. I                                 | Kellehe<br>BY<br>in<br>BY         | 1                  |          |                  | 4                   | 5<br>DI            | 6<br>EFEN<br>CC              | 7<br>SE SI<br>DLUM<br>http | 8<br>UPPL<br>IBUS,<br>o://ww | 9<br>Y CE<br>OHIO | 10<br>NTER<br>O 432<br>cc.dla | 11<br>R COL<br>218-39<br>a.mil           | 12<br>UMB<br>990          | 13        | 1   |

| SHEET REV SHEET REV STATUS OF SHEETS PMIC N/A  STAI MICRO DRA  THIS DRAWIIFOR USE BY A AND AGEI | NDAF<br>OCIRO<br>AWIN<br>NG IS A<br>ILL DEP<br>NCIES O | RD<br>CUIT<br>G<br>VAILAI<br>ARTMI | BLE<br>ENTS      | SHEI<br>PREF<br>Mar<br>CHEC<br>Ray<br>APPR<br>Micl         | PARED Picia B. I<br>CKED E<br>Monni<br>ROVED<br>hael A. | Kellehe<br>BY<br>in<br>BY<br>Frye | 1                  | 2        |                  | MICI<br>D-TY        | DI<br>ROCI         | 6<br>EFEN<br>CC              | 7<br>SE SI<br>DLUM<br>http | 8 UPPL IBUS, D://ww          | 9 Y CE OHIC vw.ds | 10  NTER  O 432  CCC.dl       | 11<br>R COL<br>218-39<br>a.mil           | 12<br>LUMB<br>990<br>MOS, | 13 US HEX | 1   |

| SHEET REV SHEET REV STATUS OF SHEETS PMIC N/A STAI MICRO DRA THIS DRAWIIFOR USE BY A            | NDAF<br>OCIRO<br>AWIN<br>NG IS A<br>ILL DEP<br>NCIES O | RD<br>CUIT<br>G<br>VAILAI<br>ARTMI | BLE<br>ENTS      | SHEE<br>PREF<br>Mar<br>CHEC<br>Ray<br>APPR<br>Micl<br>DRAV | PARED Picia B. I<br>CKED E<br>Monni<br>ROVED<br>hael A. | Kellehe  BY BY Frye  APPRO 88-1   | 1<br>r             | 2        |                  | MICI<br>D-TY<br>CON | DI<br>ROCI         | 6  EFEN CC  RCUI FLIP-F IBLE | 7 SE SI DLUM http T, DIC   | 8 UPPLIBUS, DITAL WITH TS, M | 9 Y CE OHIC vw.ds | 10  NTER O 432 cc.dl          | 218-39<br>a.mil<br>ED C<br>RESE<br>C SIL | 12<br>LUMB<br>990<br>MOS, | 13 US HEX | 1   |

DSCC FORM 2233 APR 97

# 1. SCOPE

- 1.1 <u>Scope</u>. This drawing documents two product assurance class levels consisting of high reliability (device classes Q and M) and space application (device class V). A choice of case outlines and lead finishes are available and are reflected in the Part or Identifying Number (PIN). When available, a choice of Radiation Hardness Assurance (RHA) levels are reflected in the PIN.

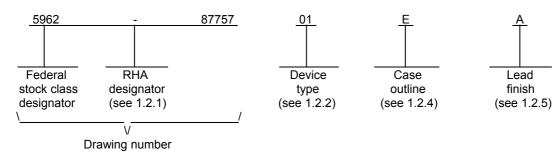

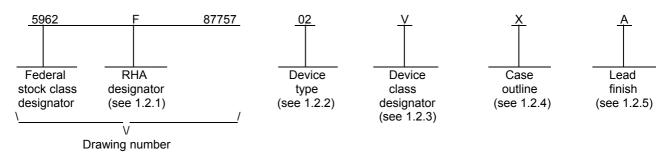

- 1.2 PIN. The PIN is as shown in the following example:

For device classes M and Q:

For device class V:

- 1.2.1 RHA designator. Device classes Q and V RHA marked devices meet the MIL-PRF-38535 specified RHA levels and are marked with the appropriate RHA designator. Device class M RHA marked devices meet the MIL-PRF-38535, appendix A specified RHA levels and are marked with the appropriate RHA designator. A dash (-) indicates a non-RHA device.

- 1.2.2 <u>Device type(s)</u>. The device type(s) identify the circuit function as follows:

| Device type | Generic number | Circuit function                                              |

|-------------|----------------|---------------------------------------------------------------|

| 01          | 54ACT174       | Hex D-type flip-flop with master reset, TTL compatible inputs |

| 02          | 54ACT174       | Hex D-type flip-flop with master reset, TTL compatible inputs |

1.2.3 <u>Device class designator</u>. The device class designator is a single letter identifying the product assurance level as listed below. Since the device class designator has been added after the original issuance of this drawing, device classes M and Q designators will not be included in the PIN and will not be marked on the device.

| Device class | <u>Device requirements documentation</u>                                                                                                                  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| М            | Vendor self-certification to the requirements for MIL-STD-883 compliant, non-JAN class level B microcircuits in accordance with MIL-PRF-38535, appendix A |

| Q or V       | Certification and qualification to MIL-PRF-38535                                                                                                          |

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-87757 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>B | SHEET 2    |

| 1 2 4 Case outline(s) | The case outline(s) are | as designated in MII | -STD-1835 and as follows: |

|-----------------------|-------------------------|----------------------|---------------------------|

| Outline letter | Descriptive designator | <u>Terminals</u> | Package style                |

|----------------|------------------------|------------------|------------------------------|

| Е              | GDIP1-T16 or CDIP2-T16 | 16               | Dual-in-line                 |

| F              | GDFP2-F16 or CDFP3-F16 | 16               | Flat pack                    |

| Χ              | CDFP4-F16              | 16               | Flat pack                    |

| 2              | CQCC1-N20              | 20               | Square leadless chip carrier |

1.2.5 <u>Lead finish</u>. The lead finish is as specified in MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

# 1.3 Absolute maximum ratings. 1/ 2/ 3/

| Supply voltage range (V <sub>CC</sub> )                                           | 0.5 V dc to +6.0 V dc                           |

|-----------------------------------------------------------------------------------|-------------------------------------------------|

| DC input voltage range (V <sub>IN</sub> )                                         | $\dots$ -0.5 V dc to V <sub>CC</sub> + 0.5 V dc |

| DC output voltage range (V <sub>OUT</sub> )                                       | $\dots$ -0.5 V dc to V <sub>CC</sub> + 0.5 V dc |

| Clamp diode current (I <sub>IK</sub> , I <sub>OK</sub> )                          | ±20 mA                                          |

| DC output current (I <sub>OUT</sub> )                                             | ±50 mA                                          |

| DC V <sub>CC</sub> or GND current (per pin) (I <sub>CC</sub> , I <sub>GND</sub> ) |                                                 |

| Maximum power dissipation (P <sub>D</sub> )                                       | 500 mW                                          |

| Storage temperature range (T <sub>STG</sub> )                                     | 65°C to +150°C                                  |

| Lead temperature (soldering, 10 seconds):                                         |                                                 |

| Case outline X                                                                    | +260°C                                          |

| Other case outlines (except case outline X)                                       | +245°C                                          |

| Thermal resistance, junction-to-case ( $\theta_{JC}$ )                            | See MIL-STD-1835                                |

| Junction temperature (T <sub>J</sub> )                                            | 175°C <u>4</u> /                                |

# 1.4 Recommended operating conditions. 2/ 3/

| Supply voltage range (V <sub>CC</sub> )                    | 0.0 V dc to V <sub>CC</sub> |

|------------------------------------------------------------|-----------------------------|

| Input rise or fall time rate ( $\Delta t/\Delta V$ ):      | o.o v do to v <sub>CC</sub> |

| V <sub>CC</sub> = 4.5 V to 5.5 V                           | 0 to 8 ns/V                 |

| Case operating temperature range (T <sub>C</sub> )         | -55°C to +125°C             |

| Minimum setup time, Dn to CP (t <sub>s</sub> ):            |                             |

| V <sub>CC</sub> = 4.5 V, T <sub>C</sub> = +25°C            | 3.0 ns                      |

| V <sub>CC</sub> = 4.5 V, T <sub>C</sub> = -55°C and +125°C | 3.0 ns                      |

| Minimum hold time, Dn to CP (t <sub>h</sub> ):             |                             |

| $V_{CC} = 4.5 \text{ V}, T_{C} = +25^{\circ}\text{C}$      | 2.0 ns                      |

| V <sub>CC</sub> = 4.5 V, T <sub>C</sub> = -55°C and +125°C | 2.5 ns                      |

| Minimum pulse width, CP (t <sub>w</sub> ):                 |                             |

| $V_{CC} = 4.5 \text{ V}, T_{C} = +25^{\circ}\text{C}$      | 5.0 ns                      |

| V <sub>CC</sub> = 4.5 V, T <sub>C</sub> = -55°C and +125°C | 6.2 ns                      |

| Minimum pulse width, $\overline{MR}$ (t <sub>w</sub> ):    |                             |

| $V_{CC} = 4.5 \text{ V}, T_{C} = +25^{\circ}\text{C}$      | 5.0 ns                      |

| V <sub>CC</sub> = 4.5 V, T <sub>C</sub> = -55°C and +125°C | 5.0 ns                      |

<sup>1/</sup> Stresses above the absolute maximum rating may cause permanent damage to the device. Extended operation at the maximum levels may degrade performance and affect reliability.

<sup>4/</sup> Maximum junction temperature shall not be exceeded except for allowable short duration burn-in screening conditions in accordance with method 5004 of MIL-STD-883.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-87757 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | B              | 3          |

<sup>2/</sup> Unless otherwise specified, all voltages are referenced to GND.

The limits for the parameters specified herein shall apply over the full specified V<sub>CC</sub> range and case temperature range of -55°C to +125°C.

# 1.4 Recommended operating conditions - Continued. 2/ 3/

Minimum recovery time,  $\overline{MR}$  to CP ( $t_{rec}$ ):

$V_{CC} = 4.5 \text{ V}, T_{C} = +25^{\circ}\text{C}$  1.5 ns  $V_{CC} = 4.5 \text{ V}, T_{C} = -55^{\circ}\text{C}$  and  $+125^{\circ}\text{C}$  1.5 ns

Maximum frequency, CP (f<sub>MAX</sub>):

# 1.5 Radiation features.

Device type 02:

#### 2. APPLICABLE DOCUMENTS

2.1 <u>Government specification, standards, and handbooks</u>. The following specification, standards, and handbooks form a part of this drawing to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

# DEPARTMENT OF DEFENSE SPECIFICATION

MIL-PRF-38535 - Integrated Circuits, Manufacturing, General Specification for.

#### DEPARTMENT OF DEFENSE STANDARDS

MIL-STD-883 - Test Method Standard Microcircuits.

MIL-STD-1835 - Interface Standard Electronic Component Case Outlines.

# DEPARTMENT OF DEFENSE HANDBOOKS

MIL-HDBK-103 - List of Standard Microcircuit Drawings.

MIL-HDBK-780 - Standard Microcircuit Drawings.

(Copies of these documents are available online at http://assist.daps.dla.mil/quicksearch/ or http://assist.daps.dla.mil or from the Standardization Document Order Desk, 700 Robbins Avenue, Building 4D, Philadelphia, PA 19111-5094.)

2.2 <u>Non-Government publications</u>. The following document(s) form a part of this document to the extent specified herein. Unless otherwise specified, the issues of these documents are those cited in the solicitation or contract.

# **ELECTRONIC INDUSTRIES ALLIANCE (EIA)**

JEDEC Standard No. 20 - Standard for Description of 54/74ACXXXX and 54/74ACTXXXX Advanced High-Speed CMOS Devices.

(Copies of these documents are available online at http://www.jedec.org or from Electronic Industries Alliance, 2500 Wilson Boulevard, Arlington, VA 22201-3834.)

2.3 <u>Order of precedence</u>. In the event of a conflict between the text of this drawing and the references cited herein, the text of this drawing takes precedence. Nothing in this document, however, supersedes applicable laws and regulations unless a specific exemption has been obtained.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-87757 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>B | SHEET 4    |

#### 3. REQUIREMENTS

- 3.1 <u>Item requirements</u>. The individual item requirements for device classes Q and V shall be in accordance with MIL-PRF-38535 and as specified herein or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. The individual item requirements for device class M shall be in accordance with MIL-PRF-38535, appendix A for non-JAN class level B devices and as specified herein.

- 3.2 <u>Design, construction, and physical dimensions</u>. The design, construction, and physical dimensions shall be as specified in MIL-PRF-38535 and herein for device classes Q and V or MIL-PRF-38535, appendix A and herein for device class M.

- 3.2.1 Case outlines. The case outlines shall be in accordance with 1.2.4 herein.

- 3.2.2 Terminal connections. The terminal connections shall be as specified on figure 1.

- 3.2.3 Truth table. The truth table shall be as specified on figure 2.

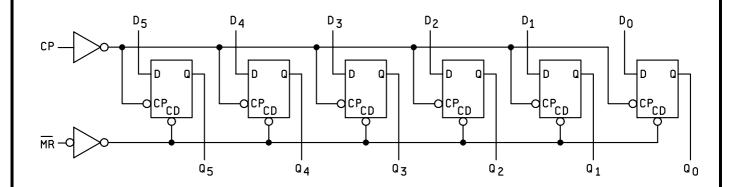

- 3.2.4 Logic diagram. The logic diagram shall be as specified on figure 3.

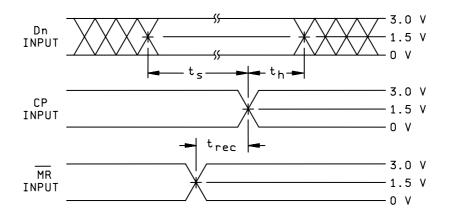

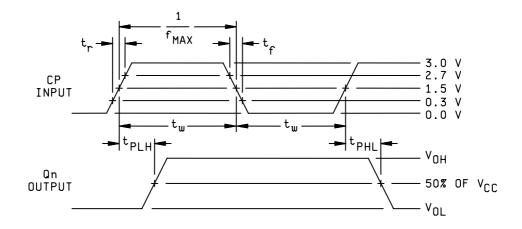

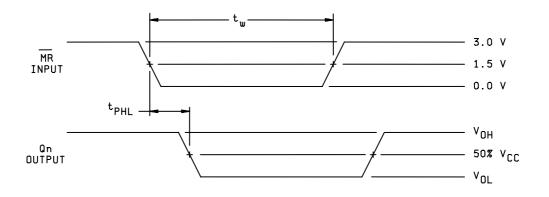

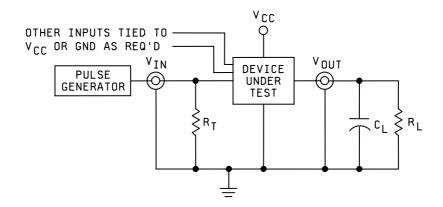

- 3.2.5 Switching waveforms and test circuit. The switching waveforms and test circuit shall be as specified on figure 4.

- 3.2.6 <u>Radiation exposure circuit</u>. The radiation exposure circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request.

- 3.3 <u>Electrical performance characteristics and postirradiation parameter limits</u>. Unless otherwise specified herein, the electrical performance characteristics and post irradiation parameter limits are as specified in table I and shall apply over the full case operating temperature range.

- 3.4 <u>Electrical test requirements</u>. The electrical test requirements shall be the subgroups specified in table II. The electrical tests for each subgroup are defined in table I.

- 3.5 <u>Marking</u>. The part shall be marked with the PIN listed in 1.2 herein. In addition, the manufacturer's PIN may also be marked. For packages where marking of the entire SMD PIN number is not feasible due to space limitations, the manufacturer has the option of not marking the "5962-" on the device. For RHA product using this option, the RHA designator shall still be marked. Marking for device classes Q and V shall be in accordance with MIL-PRF-38535. Marking for device class M shall be in accordance with MIL-PRF-38535, appendix A.

- 3.5.1 <u>Certification/compliance mark</u>. The certification mark for device classes Q and V shall be a "QML" or "Q" as required in MIL-PRF-38535. The compliance mark for device class M shall be a "C" as required in MIL-PRF-38535, appendix A.

- 3.6 <u>Certificate of compliance</u>. For device classes Q and V, a certificate of compliance shall be required from a QML-38535 listed manufacturer in order to supply to the requirements of this drawing (see 6.6.1 herein). For device class M, a certificate of compliance shall be required from a manufacturer in order to be listed as an approved source of supply in MIL-HDBK-103 (see 6.6.2 herein). The certificate of compliance submitted to DSCC-VA prior to listing as an approved source of supply for this drawing shall affirm that the manufacturer's product meets, for device classes Q and V, the requirements of MIL-PRF-38535 and herein or for device class M, the requirements of MIL-PRF-38535, appendix A and herein.

- 3.7 <u>Certificate of conformance</u>. A certificate of conformance as required for device classes Q and V in MIL-PRF-38535 or for device class M in MIL-PRF-38535, appendix A shall be provided with each lot of microcircuits delivered to this drawing.

- 3.8 <u>Notification of change for device class M</u>. For device class M, notification to DSCC-VA of change of product (see 6.2 herein) involving devices acquired to this drawing is required for any change that affects this drawing.

- 3.9 <u>Verification and review for device class M.</u> For device class M, DSCC, DSCC's agent, and the acquiring activity retain the option to review the manufacturer's facility and applicable required documentation. Offshore documentation shall be made available onshore at the option of the reviewer.

- 3.10 <u>Microcircuit group assignment for device class M</u>. Device class M devices covered by this drawing shall be in microcircuit group number 38 (see MIL-PRF-38535, appendix A).

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-87757 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>B | SHEET 5    |

|                                                   |                   | TABLE I. <u>Electrical performan</u>                                                                                                       |                       |                 |                   |          |                |          |

|---------------------------------------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------|-------------------|----------|----------------|----------|

| Test and<br>MIL-STD-883<br>test method <u>1</u> / | Symbol            | Test conditions $\underline{2}/\underline{3}/$<br>-55°C $\leq$ T <sub>C</sub> $\leq$ +125°C<br>+4.5 V $\leq$ V <sub>CC</sub> $\leq$ +5.5 V | Device<br>type<br>and | V <sub>CC</sub> | Group A subgroups | Limi     | its <u>4</u> / | Unit     |

|                                                   |                   | unless otherwise specified                                                                                                                 | device<br>class       |                 |                   | Min      | Max            |          |

| Positive input clamp voltage 3022                 | V <sub>IC+</sub>  | For input under test, I <sub>IN</sub> = 1.0 mA                                                                                             | All<br>V              | 0.0 V           | 1                 | 0.4      | 1.5            | V        |

| Negative input clamp voltage 3022                 | V <sub>IC</sub> - | For input under test, I <sub>IN</sub> = -1.0 mA                                                                                            | All<br>V              | Open            | 1                 | -0.4     | -1.5           | V        |

| High level output                                 | V <sub>OH</sub>   | V <sub>IN</sub> = V <sub>IH</sub> minimum or V <sub>IL</sub> maximum                                                                       | All                   | 4.5 V           | 1, 2, 3           | 4.4      |                | V        |

| voltage<br>3006                                   | <u>5</u> /        | I <sub>OH</sub> = -50 μA                                                                                                                   | All                   | 5.5 V           |                   | 5.4      |                |          |

|                                                   |                   | $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum                                                                                              | All                   | 4.5 V           | 1, 2, 3           | 3.70     |                |          |

|                                                   |                   | I <sub>OH</sub> = -24 mA                                                                                                                   | All                   | 5.5 V           | 1, 2, 3           | 4.70     |                |          |

|                                                   |                   | $V_{IN}$ = $V_{IH}$ minimum or $V_{IL}$ maximum $I_{OH}$ = -50 mA                                                                          | All<br>All            | 5.5 V           | 1, 2, 3           | 3.85     |                |          |

| Low level output                                  | V <sub>OL</sub>   | $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum                                                                                              | All                   | 4.5 V           | 1, 2, 3           |          | 0.1            | ٧        |

| voltage<br>3007                                   | <u>5</u> /        | I <sub>OL</sub> = 50 μA                                                                                                                    | All                   | 5.5 V           |                   |          | 0.1            |          |

|                                                   |                   | $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum                                                                                              | All                   | 4.5 V           | 1, 2, 3           |          | 0.50           |          |

|                                                   |                   | I <sub>OL</sub> = 24 mA                                                                                                                    | All                   | 5.5 V           | 1, 2, 3           | <u> </u> | 0.50           |          |

|                                                   |                   | $V_{IN} = V_{IH}$ minimum or $V_{IL}$ maximum $I_{OL} = 50$ mA                                                                             | AII<br>AII            | 5.5 V           | 1, 2, 3           |          | 1.65           |          |

| High level input                                  | V <sub>IH</sub>   |                                                                                                                                            | All                   | 4.5 V           | 1, 2, 3           | 2.0      |                | V        |

| voltage                                           | <u>6</u> /        |                                                                                                                                            | All                   | 5.5 V           |                   | 2.0      |                |          |

| Low level input                                   | V <sub>IL</sub>   |                                                                                                                                            | AII<br>AII            | 4.5 V           | 1, 2, 3           |          | 8.0            | V        |

| voltage                                           | <u>6</u> /        |                                                                                                                                            | Aii                   | 5.5 V           |                   |          | 8.0            | <u> </u> |

| Input leakage<br>current high<br>3010             | I <sub>IH</sub>   | For input under test, $V_{IN} = V_{CC}$<br>For all other inputs,<br>$V_{IN} = V_{CC}$ or GND                                               | All<br>All            | 5.5 V           | 1, 2, 3           |          | 1.0            | μА       |

| Input leakage<br>current low<br>3009              | I <sub>IL</sub>   | For input under test, $V_{IN}$ = GND<br>For all other inputs,<br>$V_{IN}$ = $V_{CC}$ or GND                                                | All<br>All            | 5.5 V           | 1, 2, 3           |          | -1.0           | μА       |

| Quiescent supply current, output                  | I <sub>CCH</sub>  | V <sub>IN</sub> = V <sub>CC</sub> or GND                                                                                                   | 01<br>All             | 5.5 V           | 1, 2, 3           |          | 160.0          | μА       |

| high<br>3005                                      |                   |                                                                                                                                            | 02                    | ]               | 1                 |          | 2.0            |          |

|                                                   |                   |                                                                                                                                            | All                   |                 | 2, 3              |          | 160.0          |          |

|                                                   |                   | M, D, P, L, R, F<br>7/                                                                                                                     | 02<br>Q, V            | 5.5 V           | 1                 |          | 50.0           |          |

See footnotes at end of table.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-87757 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | B              | 6          |

|                                                                |                                  | TABLE I. Electric                                                                                         | cal performance cha            | aracteristics                                      | - Contini | ued.           |                    |       |    |

|----------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------|-----------|----------------|--------------------|-------|----|

| Test and MIL-STD-883 test method 1/                            | Symbol                           | Test conditi<br>$-55^{\circ}\text{C} \le \text{T}_{\text{C}}$<br>$+4.5 \text{ V} \le \text{V}_{\text{C}}$ | <sub>5</sub> ≤ +125°C          | Device V <sub>CC</sub> Group A Limit subgroups and |           | its <u>4</u> / | :s <u>4</u> / Unit |       |    |

| test method <u>h</u>                                           |                                  | unless otherw                                                                                             |                                | device<br>class                                    |           |                | Min                | Max   |    |

| Quiescent supply current, output                               | I <sub>CCL</sub>                 | $V_{IN} = V_{CC}$ or GND                                                                                  |                                | 01<br>All                                          | 5.5 V     | 1, 2, 3        |                    | 160.0 | μА |

| low<br>3005                                                    |                                  |                                                                                                           | •                              | 02                                                 |           | 1              |                    | 2.0   |    |

|                                                                |                                  |                                                                                                           |                                | All                                                | '         | 2, 3           |                    | 160.0 |    |

|                                                                |                                  |                                                                                                           | M, D, P, L, R, F<br><u>7</u> / | 02<br>Q, V                                         | 5.5 V     | 1              |                    | 50.0  |    |

| Quiescent supply<br>current delta, TTL<br>input levels<br>3005 | ΔI <sub>CC</sub> <u>8</u> /      | For input under tes $V_{IN} = V_{CC} - 2.1 \text{ V}$ For all other inputs $V_{IN} = V_{CC}$ or GND       | 5,                             | All<br>All                                         | 5.5 V     | 1, 2, 3        |                    | 1.6   | mA |

| Input capacitance 3012                                         | C <sub>IN</sub>                  | T <sub>C</sub> = 25°C<br>See 4.4.1c                                                                       |                                | All<br>All                                         | GND       | 4              |                    | 10    | pF |

| Power dissipation capacitance                                  | C <sub>PD</sub> 9/               | T <sub>C</sub> = 25°C<br>See 4.4.1c                                                                       |                                | All<br>All                                         | 5.0 V     | 4              |                    | 60    | pF |

| Functional tests                                               | <u>10</u> /                      | $V_{IN} = V_{IH}$ or $V_{IL}$                                                                             |                                | All                                                | 4.5 V     | 7, 8           | L                  | Н     |    |

| 3014                                                           |                                  | Verify output V <sub>OUT</sub><br>See 4.4.1b                                                              |                                | All                                                | 5.5 V     | 7, 8           | L                  | Н     |    |

| Propagation delay                                              | t <sub>PHL1</sub> ,              | C <sub>L</sub> = 50 pF minimu                                                                             | ım                             | All                                                | 4.5 V     | 9              | 1.0                | 10.5  | ns |

| time, CP to Qn<br>3003                                         | t <sub>PLH1</sub><br><u>11</u> / | $R_L = 500\Omega$<br>See figure 4                                                                         |                                | All                                                |           | 10, 11         | 1.0                | 14.0  |    |

| Propagation delay                                              | t <sub>PHL2</sub>                | ]                                                                                                         | •                              | All                                                | 4.5 V     | 9              | 1.0                | 11.5  | ns |

| time, MR to Qn<br>3003                                         | 11/                              |                                                                                                           | ,                              | All                                                |           | 10, 11         | 1.0                | 15.5  |    |

- 1/ For tests not listed in the referenced MIL-STD-883, [e.g. V<sub>IH</sub>, V<sub>IL</sub>], utilize the general test procedure under the conditions listed herein.

- $\underline{2}'$  Each input/output, as applicable, shall be tested at the specified temperature, for the specified limits, to the tests in table I herein. Output terminals not designated shall be high level logic, low level logic, or open, except for all  $I_{CC}$  and  $\Delta I_{CC}$  tests, the output terminal shall be open. When performing these tests, the current meter shall be placed in the circuit such that all current flows through the meter.

- 3/ RHA parts for device type 02 meet all levels M, D, P, L, R, and F of irradiation. However, these parts are only tested at the "F" level. Pre and post irradiation values are identical unless otherwise specified in table I. When performing post irradiation electrical measurements for any RHA level, T<sub>A</sub> = 25°C.

- 4/ For negative and positive voltage and current values, the sign designates the potential difference in reference to GND and the direction of current flow, respectively; and the absolute value of the magnitude, not the sign, is relative to the minimum and maximum limits, as applicable, listed herein. All devices shall meet or exceed the limits specified in table I, as applicable, at 4.5 V ≤ V<sub>CC</sub> ≤ 5.5 V.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-87757 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>B | SHEET 7    |

# TABLE I. Electrical performance characteristics - Continued.

- 5/ The V<sub>OH</sub> and V<sub>OL</sub> tests shall be tested at V<sub>CC</sub> = 4.5 V. The V<sub>OH</sub> and V<sub>OL</sub> tests are guaranteed, if not tested, for V<sub>CC</sub> = 5.5 V. Limits shown apply to operation at V<sub>CC</sub> = 5.0 V  $\pm$ 0.5 V. Transmission driving tests are performed at V<sub>CC</sub> = 5.5 V with a 2 ms duration maximum. This test may be performed using V<sub>IN</sub> = V<sub>CC</sub> or GND. When V<sub>IN</sub> = V<sub>CC</sub> or GND is used, the test is guaranteed for V<sub>IN</sub> = V<sub>IH</sub> minimum and V<sub>IL</sub> maximum.

- $\underline{6}'$  The  $V_{IH}$  and  $V_{IL}$  tests are not required if applied as forcing functions for  $V_{OH}$  and  $V_{OL}$  tests.

- 7/ The maximum limit for this parameter at 100 krads (Si) is 2  $\mu$ A.

- 8/ This test may be performed either one input at a time (preferred method) or with all input pins simultaneously at  $V_{IN} = V_{CC} 2.1 \text{ V}$  (alternate method). Classes Q and V shall use the preferred method. When the test is performed using the alternate test method, the maximum limit is equal to the number of inputs at a high TTL input level times  $\Delta I_{CC}$  maximum limit; and the preferred method and limits are guaranteed.

- 9/ Power dissipation capacitance ( $C_{PD}$ ) determines both the power consumption ( $P_D$ ) and dynamic current consumption ( $I_S$ ). Where:

$$\begin{aligned} P_{D} &= (C_{PD} + C_{L}) (V_{CC} \times V_{CC}) f + (I_{CC} \times V_{CC}) + (n \times d \times \Delta I_{CC} \times V_{CC}) \\ I_{S} &= (C_{PD} + C_{L}) V_{CC} f + I_{CC} + (n \times d \times \Delta I_{CC}) \end{aligned}$$

For both  $P_D$  and  $I_S$ , n is number of device inputs at TTL levels; f is the frequency of the input signal; d is duty cycle of the input signal; and  $C_L$  is the external output load capacitance.

- 10/ Tests shall be performed in sequence, attributes data only. Functional tests shall include the truth table and other logic patterns used for fault detection. The test vectors used to verify the truth table shall, at a minimum, test all functions of each input and output. All possible input to output logic patterns per function shall be guaranteed, if not tested, to the truth table in figure 2 herein. Functional tests shall be performed in sequence as approved by the qualifying activity on qualified devices. Allowable tolerances in accordance with MIL-STD-883 for the input voltage levels may be incorporated. For outputs, H ≥ 2.5 V, L < 2.5 V.</p>

- 11/ AC limits at V<sub>CC</sub> = 5.5 V are equal to the limits at V<sub>CC</sub> = 4.5 V and guaranteed by testing at V<sub>CC</sub> = 4.5 V. Minimum AC limits for V<sub>CC</sub> = 5.5 V are 1.0 ns and guaranteed by guardbanding the V<sub>CC</sub> = 4.5 V minimum limits to 1.5 ns. For propagation delay tests, all paths must be tested.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-87757 |

|-------------------------------------------------------------|-----------|---------------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>B | SHEET 8    |

| Device<br>types | 01, 02             |                 |  |

|-----------------|--------------------|-----------------|--|

| Case outlines   | E, F, X            | 2               |  |

| Terminal number | Terminal<br>symbol | Terminal symbol |  |

| 1               | MR                 | NC              |  |

| 2               | Q0                 | MR              |  |

| 3               | D0                 | Q0              |  |

| 4               | D1                 | D0              |  |

| 5               | Q1                 | D1              |  |

| 6               | D2                 | NC              |  |

| 7               | Q2                 | Q1              |  |

| 8               | GND                | D2              |  |

| 9               | СР                 | Q2              |  |

| 10              | Q3                 | GND             |  |

| 11              | D3                 | NC              |  |

| 12              | Q4                 | СР              |  |

| 13              | D4                 | Q3              |  |

| 14              | D5                 | D3              |  |

| 15              | Q5                 | Q4              |  |

| 16              | V <sub>CC</sub>    | NC              |  |

| 17              |                    | D4              |  |

| 18              |                    | D5              |  |

| 19              |                    | Q5              |  |

| 20              |                    | V <sub>CC</sub> |  |

NC = No connection

FIGURE 1. <u>Terminal connections</u>.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-87757 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | B              | 9          |

|    | Inputs |    | Outputs |

|----|--------|----|---------|

| MR | СР     | Dn | Qn      |

| L  | Х      | Х  | L       |

| Н  | 1      | Н  | Н       |

| Н  | 1      | L  | L       |

| Н  | L      | Х  | Q0      |

H = High voltage level L = Low voltage level

X = Irrelevant

↑ = Low-to-high clock transition

Q0 = The level of Q before the low-to-high transition of clock

FIGURE 2. Truth table.

FIGURE 3. Logic diagram.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-87757 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | A              | 10         |

FIGURE 4. Switching waveforms and test circuit.

| STANDARD<br>MICROCIRCUIT DRAWING                            | SIZE<br>A |                     | 5962-87757  |

|-------------------------------------------------------------|-----------|---------------------|-------------|

| DEFENSE SUPPLY CENTER COLUMBUS<br>COLUMBUS, OHIO 43218-3990 |           | REVISION LEVEL<br>B | SHEET<br>11 |

# NOTES:

- 1.  $C_L = 50 \text{ pF minimum or equivalent (includes test jig and probe capacitance)}$ .

- R<sub>T</sub> = 50Ω or equivalent, R<sub>L</sub> = 500Ω or equivalent.

Input signal from pulse generator: V<sub>IN</sub> = 0.0 V to 3.0 V; PRR ≤ 10 MHz; t<sub>r</sub> ≤ 3.0 ns; t<sub>f</sub> ≤ 3.0 ns; t<sub>f</sub> and t<sub>f</sub> shall be measured from 0.3 V to 2.7 V and from 2.7 V to 0.3 V, respectively; duty cycle = 50 percent.

- 4. Timing parameters shall be tested at a minimum input frequency of 1 MHz.

- 5. The outputs are measured one at a time with one transition per measurement.

FIGURE 4. Switching waveforms and test circuit - Continued.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-87757 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | B              | 12         |

#### 4. VERIFICATION

- 4.1 <u>Sampling and inspection</u>. For device classes Q and V, sampling and inspection procedures shall be in accordance with MIL-PRF-38535 or as modified in the device manufacturer's Quality Management (QM) plan. The modification in the QM plan shall not affect the form, fit, or function as described herein. For device class M, sampling and inspection procedures shall be in accordance with MIL-PRF-38535, appendix A.

- 4.2 <u>Screening</u>. For device classes Q and V, screening shall be in accordance with MIL-PRF-38535, and shall be conducted on all devices prior to qualification and technology conformance inspection. For device class M, screening shall be in accordance with method 5004 of MIL-STD-883, and shall be conducted on all devices prior to quality conformance inspection.

- 4.2.1 Additional criteria for device class M.

- a. Burn-in test, method 1015 of MIL-STD-883.

- (1) Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015 of MIL-STD-883.

- (2)  $T_A = +125^{\circ}C$ , minimum.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

# 4.2.2 Additional criteria for device classes Q and V.

- a. The burn-in test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The burn-in test circuit shall be maintained under document revision level control of the device manufacturer's Technology Review Board (TRB) in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1015 of MIL-STD-883.

- b. Interim and final electrical test parameters shall be as specified in table II herein.

- Additional screening for device class V beyond the requirements of device class Q shall be as specified in MIL-PRF-38535, appendix B.

- 4.3 <u>Qualification inspection for device classes Q and V</u>. Qualification inspection for device classes Q and V shall be in accordance with MIL-PRF-38535. Inspections to be performed shall be those specified in MIL-PRF-38535 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

- 4.4 <u>Conformance inspection</u>. Technology conformance inspection for classes Q and V shall be in accordance with MIL-PRF-38535 including groups A, B, C, D, and E inspections and as specified herein. Quality conformance inspection for device class M shall be in accordance with MIL-PRF-38535, appendix A and as specified herein. Inspections to be performed for device class M shall be those specified in method 5005 of MIL-STD-883 and herein for groups A, B, C, D, and E inspections (see 4.4.1 through 4.4.4).

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-87757 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | B              | 13         |

# TABLE II. Electrical test requirements.

| Test requirements                                 | Subgroups<br>(in accordance with<br>MIL-STD-883, method<br>5005, table I) | Subgroups<br>(in accordance with<br>MIL-PRF-38535, table III) |                                                |

|---------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------|

|                                                   | Device<br>class M                                                         | Device<br>class Q                                             | Device<br>class V                              |

| Interim electrical parameters (see 4.2)           |                                                                           |                                                               | 1                                              |

| Final electrical parameters (see 4.2)             | <u>1</u> / 1, 2, 3, 7, 8, 9                                               | <u>1</u> / 1, 2, 3, 7, 8, 9                                   | <u>2</u> / <u>3</u> / 1, 2, 3, 7, 8, 9, 10, 11 |

| Group A test requirements (see 4.4)               | 1, 2, 3, 4, 7,<br>8, 9, 10, 11                                            | 1, 2, 3, 4, 7,<br>8, 9, 10, 11                                | 1, 2, 3, 4, 7,<br>8, 9, 10, 11                 |

| Group C end-point electrical parameters (see 4.4) | 1, 2, 3                                                                   | 1, 2, 3                                                       | <u>3</u> / 1, 2, 3, 7,<br>8, 9, 10, 11         |

| Group D end-point electrical parameters (see 4.4) | 1, 2, 3                                                                   | 1, 2, 3                                                       | 1, 2, 3                                        |

| Group E end-point electrical parameters (see 4.4) | 1, 7, 9                                                                   | 1, 7, 9                                                       | 1, 7, 9                                        |

- 1/ PDA applies to subgroup 1.

2/ PDA applies to subgroups 1, 7, and deltas.

3/ Delta limits, as specified in table III, shall be required where specified, and the delta limits shall be completed with reference to the zero hour electrical parameters.

TABLE III. Burn-in and operating life test, delta parameters (+25°C).

| Parameter 1/                                                                  | Symbol                              | Device<br>type | Delta limits |

|-------------------------------------------------------------------------------|-------------------------------------|----------------|--------------|

| Quiescent supply current                                                      | I <sub>CCH</sub> , I <sub>CCL</sub> | 02             | ±300 nA      |

| Supply current delta                                                          | $\Delta I_{CC}$                     | 02             | ±0.4 mA      |

| Input current low level                                                       | I <sub>IL</sub>                     | 02             | ±20 nA       |

| Input current high level                                                      | I <sub>IH</sub>                     | 02             | ±20 nA       |

| Output voltage low level (V <sub>CC</sub> = 5.5 V, I <sub>OL</sub> = 24 mA)   | V <sub>OL</sub>                     | 02             | ±0.04 V      |

| Output voltage high level (V <sub>CC</sub> = 5.5 V, I <sub>OH</sub> = -24 mA) | V <sub>OH</sub>                     | 02             | ±0.20 V      |

1/ These parameters shall be recorded before and after the required burn-in and life tests to determined delta limits.

| STANDARD  MICROCIRCUIT DRAWING  DEFENSE SUPPLY CENTER COLUMBUS  COLUMBUS, OHIO 43218-3990 | SIZE<br>A |                     | 5962-87757  |

|-------------------------------------------------------------------------------------------|-----------|---------------------|-------------|

|                                                                                           |           | REVISION LEVEL<br>B | SHEET<br>14 |

# 4.4.1 Group A inspection

- a. Tests shall be as specified in table II herein.

- b. For device class M, subgroups 7 and 8 tests shall be sufficient to verify the truth table in figure 2 herein. The test vectors used to verify the truth table shall, at a minimum, test all functions of each input and output. All possible input to output logic patterns per function shall be guaranteed, if not tested, to the truth table in figure 2 herein. For device classes Q and V, subgroups 7 and 8 shall include verifying the functionality of the device.

- c. C<sub>IN</sub> and C<sub>PD</sub> shall be measured only for initial qualification and after process or design changes which may affect capacitance. C<sub>IN</sub> shall be measured between the designated terminal and GND at a frequency of 1 MHz. C<sub>PD</sub> shall be tested in accordance with the latest revision of JEDEC Standard No. 20 and table I herein. For C<sub>IN</sub> and C<sub>PD</sub>, test all applicable pins on five devices with zero failures.

- 4.4.2 Group C inspection. The group C inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.2.1 Additional criteria for device class M. Steady-state life test conditions, method 1005 of MIL-STD-883:

- a. Test condition A, B, C, or D. The test circuit shall be maintained by the manufacturer under document revision level control and shall be made available to the preparing or acquiring activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1005 of MIL-STD-883.

- b.  $T_A = +125$ °C, minimum.

- c. Test duration: 1,000 hours, except as permitted by method 1005 of MIL-STD-883.

- 4.4.2.2 Additional criteria for device classes Q and V. The steady-state life test duration, test condition and test temperature, or approved alternatives shall be as specified in the device manufacturer's QM plan in accordance with MIL-PRF-38535. The test circuit shall be maintained under document revision level control by the device manufacturer's TRB in accordance with MIL-PRF-38535 and shall be made available to the acquiring or preparing activity upon request. The test circuit shall specify the inputs, outputs, biases, and power dissipation, as applicable, in accordance with the intent specified in method 1005 of MIL-STD-883.

- 4.4.3 <u>Group D inspection</u>. The group D inspection end-point electrical parameters shall be as specified in table II herein.

- 4.4.4 <u>Group E inspection</u>. Group E inspection is required only for parts intended to be marked as radiation hardness assured (see 3.5 herein).

- a. End-point electrical parameters shall be as specified in table II herein.

- b. For device classes Q and V, the devices or test vehicle shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38535 for the RHA level being tested. For device class M, the devices shall be subjected to radiation hardness assured tests as specified in MIL-PRF-38535, appendix A for the RHA level being tested. All device classes must meet the postirradiation end-point electrical parameter limits as defined in table I at  $T_A = +25$ °C, after exposure, to the subgroups specified in table II herein.

- c. RHA tests for device classes M, Q, and V for levels M, D, P, L, R, and F shall be performed through each level to determine at what levels the devices meet the RHA requirements. These RHA tests shall be performed for initial qualification and after design or process changes which may affect the RHA performance of the device.

- d. Prior to irradiation, each selected sample shall be assembled in its qualified package. It shall pass the specified group A electrical parameters in table I for subgroups specified in table II herein.

| STANDARD MICROCIRCUIT DRAWING DEFENSE SUPPLY CENTER COLUMBUS COLUMBUS, OHIO 43218-3990 | SIZE<br>A |                     | 5962-87757  |

|----------------------------------------------------------------------------------------|-----------|---------------------|-------------|

|                                                                                        |           | REVISION LEVEL<br>B | SHEET<br>15 |

4.4.4.1 <u>Total dose irradiation testing</u>. Total dose irradiation testing shall be performed in accordance with MIL-STD-883, method 1019, condition A, and as specified herein. Prior to and during total dose irradiation characterization and testing, the devices for characterization shall be biased so that 50 percent are at inputs high and 50 percent are at inputs low, and the devices for testing shall be biased to the worst case condition established during characterization. Devices shall be biased as follows:

Device type 02:

- a. Inputs tested high,  $V_{CC}$  = 5.5 V dc  $\pm 5\%$ ,  $V_{IN}$  = 5.0 V dc +10%,  $R_{IN}$  = 1 k $\Omega$   $\pm 20\%$ , and all outputs are open.

- b. Inputs tested low,  $V_{CC}$  = 5.5 V dc ±5%,  $V_{IN}$  = 0.0 V,  $R_{IN}$  = 1 k $\Omega$  ±20%, and all outputs are open.

- 4.4.4.1.1 <u>Accelerated aging test</u>. Accelerated aging test shall be performed on classes M, Q, and V devices requiring an RHA level greater than 5K rads (Si). The post-anneal end-point electrical parameter limits shall be as specified in table I herein and shall be the pre-irradiation end-point electrical parameter limit at  $25^{\circ}$ C. Testing shall be performed at initial qualification and after any design or process changes which may affect the RHA response of the device.

- 4.5 Methods of inspection. Methods of inspection shall be specified as follows:

- 4.5.1 <u>Voltage and current</u>. Unless otherwise specified, all voltages given are referenced to the microcircuit GND terminal. Currents given are conventional current and positive when flowing into the referenced terminal.

- 5. PACKAGING

- 5.1 <u>Packaging requirements</u>. The requirements for packaging shall be in accordance with MIL-PRF-38535 for device classes Q and V or MIL-PRF-38535, appendix A for device class M.

- 6. NOTES

- 6.1 <u>Intended use</u>. Microcircuits conforming to this drawing are intended for use for Government microcircuit applications (original equipment), design applications, and logistics purposes.

- 6.1.1 <u>Replaceability</u>. Microcircuits covered by this drawing will replace the same generic device covered by a contractor-prepared specification or drawing.

- 6.1.2 Substitutability. Device class Q devices will replace device class M devices.

- 6.2 <u>Configuration control of SMD's</u>. All proposed changes to existing SMD's will be coordinated with the users of record for the individual documents. This coordination will be accomplished using DD Form 1692, Engineering Change Proposal.

- 6.3 <u>Record of users</u>. Military and industrial users should inform Defense Supply Center Columbus (DSCC) when a system application requires configuration control and which SMD's are applicable to that system. DSCC will maintain a record of users and this list will be used for coordination and distribution of changes to the drawings. Users of drawings covering microelectronic devices (FSC 5962) should contact DSCC-VA, telephone (614) 692-0544.

- 6.4 <u>Comments</u>. Comments on this drawing should be directed to DSCC-VA , Columbus, Ohio 43218-3990, or telephone (614) 692-0547.

- 6.5 <u>Abbreviations, symbols, and definitions</u>. The abbreviations, symbols, and definitions used herein are defined in MIL-PRF-38535 and MIL-HDBK-1331.

- 6.6 Sources of supply.

- 6.6.1 <u>Sources of supply for device classes Q and V</u>. Sources of supply for device classes Q and V are listed in QML-38535. The vendors listed in QML-38535 have submitted a certificate of compliance (see 3.6 herein) to DSCC-VA and have agreed to this drawing.

- 6.6.2 <u>Approved sources of supply for device class M.</u> Approved sources of supply for class M are listed in MIL-HDBK-103. The vendors listed in MIL-HDBK-103 have agreed to this drawing and a certificate of compliance (see 3.6 herein) has been submitted to and accepted by DSCC-VA.

| STANDARD<br>MICROCIRCUIT DRAWING | SIZE<br>A |                | 5962-87757 |

|----------------------------------|-----------|----------------|------------|

| DEFENSE SUPPLY CENTER COLUMBUS   |           | REVISION LEVEL | SHEET      |

| COLUMBUS, OHIO 43218-3990        |           | B              | 16         |

# STANDARD MICROCIRCUIT DRAWING BULLETIN DATE: 05-04-21

Approved sources of supply for SMD 5962-87757 are listed below for immediate acquisition information only and shall be added to MIL-HDBK-103 and QML-38535 during the next revision. MIL-HDBK-103 and QML-38535 will be revised to include the addition or deletion of sources. The vendors listed below have agreed to this drawing and a certificate of compliance has been submitted to and accepted by DSCC-VA. This information bulletin is superseded by the next dated revision of MIL-HDBK-103 and QML-38535. DSCC maintains an online database of all current sources of supply at http://www.dscc.dla.mil/Programs/Smcr/.

| Standard<br>microcircuit drawing<br>PIN <u>1</u> / | Vendor<br>CAGE<br>number | Vendor<br>similar<br>PIN <u>2</u> / |

|----------------------------------------------------|--------------------------|-------------------------------------|

| 5962-8775701EA                                     | 27014                    | 54ACT174DMQB                        |

| 5962-8775701FA                                     | 27014                    | 54ACT174FMQB                        |

| 5962-87757012A                                     | 27014                    | 54ACT174LMQB                        |

| 5962-8775701XA                                     | <u>3</u> /               | 54ACT174K02Q                        |

| 5962-8775701XC                                     | <u>3</u> /               | 54ACT174K01Q                        |

| 5962-8775701VXA                                    | <u>3</u> /               | 54ACT174K02V                        |

| 5962-8775701VXC                                    | <u>3</u> /               | 54ACT174K01V                        |

| 5962-8775702XA                                     | F8859                    | 54ACT174K02Q                        |

| 5962-8775702XC                                     | F8859                    | 54ACT174K01Q                        |

| 5962-8775702VXA                                    | F8859                    | 54ACT174K02V                        |

| 5962-8775702VXC                                    | F8859                    | 54ACT174K01V                        |

| 5962F8775702XA                                     | F8859                    | RHFACT174K02Q                       |

| 5962F8775702XC                                     | F8859                    | RHFACT174K01Q                       |

| 5962F8775702VXA                                    | F8859                    | RHFACT174K02V                       |

| 5962F8775702VXC                                    | F8859                    | RHFACT174K01V                       |

- The lead finish shown for each PIN representing a hermetic package is the most readily available from the manufacturer listed for that part. If the desired lead finish is not listed, contact the vendor to determine its availability.

- 2/ Caution. Do not use this number for item acquisition. Items acquired to this number may not satisfy the performance requirements of this drawing.

- 3/ No longer available from an approved source of supply.

| Vendor CAGE<br>number | Vendor name<br>and address                                                                         |

|-----------------------|----------------------------------------------------------------------------------------------------|

| 27014                 | National Semiconductor<br>2900 Semiconductor Drive<br>P.O. Box 58090<br>Santa Clara, CA 95052-8090 |

| F8859                 | ST Microelectronics<br>3 rue de Suisse<br>BP4199<br>35041 RENNES cedex2 - France                   |

The information contained herein is disseminated for convenience only and the Government assumes no liability whatsoever for any inaccuracies in the information bulletin.